Abstract

Photonic networks-on-chip (PNoCs) have emerged as a promising alternative to the conventional metal-based networks-on-chip due to their advantages in bandwidth density, power efficiency and propagation speed. Existing works on PNoCs concentrate on architectures of photonic networks with the assumption that the underlying photonic infrastructure operates correctly and reliably. However, the key optical device in PNoC systems, microring resonators (MRs), is very sensitive to temperature fluctuation and manufacturing errors. A single MR failure can cause messages to be misdelivered or lost, which results in bandwidth loss or even complete failure of the whole system. In this paper, we present a fault-tolerant Photonic Network-on-Chip architecture, named FT-PHENIC, which uses minimal redundancy to ensure accuracy of packet transmission even after faulty microring resonators (MRs) are detected. FT-PHENIC is based on a microring fault-resilient photonic router (FTTDOR) and an adaptive path-configuration and routing algorithm. Simulation results show that FT-PHENIC tolerates MR faults quite well up until around when 20 % of the MRs have failed, and has minimal bandwidth degradation and power drawbacks.

Similar content being viewed by others

Explore related subjects

Discover the latest articles and news from researchers in related subjects, suggested using machine learning.References

Adi C, Matsutani H, Koibuchi M, Irie H, Miyoshi T, Yoshinaga T (2010) An efficient path setup for a photonic network-on-chip. In: Networking and Computing (ICNC), 2010 First International Conference on, pp 156–161. doi:10.1109/IC-NC.2010.31

Agrawal GP (2012) Fiber-optic communication systems, vol 222. Wiley, New York

Ahn J, Fiorentino M, Beausoleil R, Binkert N, Davis A, Fattal D, Jouppi N, McLaren M, Santori C, Schreiber R, Spillane S, Vantrease D, Xu Q (2009) Devices and architectures for photonic chip-scale integration. Appl Phys A 95(4):989–997. doi:10.1007/s00339-009-5109-2

Ben Abdallah A (2013) Multicore systems-on-chip: practical hardware/software design, 2nd edn. Atlantis. ISBN-13:978-9491216916. http://www.amazon.com/Multicore-Systems-chip-Practical-Intelligence/dp/9078677228

Ben Abdallah A, Sowa M (2006) Basic network-on-chip interconnection for future Gigascale MCSoCs Applications: communication and computation orthogonalization. In: Proceeding of the symposium on science, society, and technology, pp 4–9

Ben Ahmed A, Ben Abdallah A (2013a) Architecture and design of high-throughput, low-latency, and fault-tolerant routing algorithm for 3D-network-on-chip (3D-NoC). J Supercomput 66(3):1507–1532. doi:10.1007/s11227-013-0940-9

Ben Ahmed A, Ben Abdallah A (2013b) Phenic: silicon photonic 3d-network-on-chip architecture for high-performance heterogeneous many-core system-on-chip. In: 2013 14th International Conference on Sciences and Techniques of Automatic Control and Computer Engineering (STA), pp 1–9. doi:10.1109/STA.2013.6914696

Ben Ahmed A, Ben Abdallah A (2014) Graceful deadlock-free fault-tolerant routing algorithm for 3d network-on-chip architectures. J Parallel Distrib Comput 74(4):2229–2240

Ben Ahmed A, Ben Abdallah A (2015) Hybrid silicon-photonic network-on-chip for future generations of high-performance many-core systems. J Supercomput. doi:10.1007/s11227-015-1539-0

Ben Ahmed A, Ben Abdallah A (2016) An energy-efficient high-throughput mesh-based photonic on-chip interconnect for many-core systems. In: Photonics, Multidisciplinary Digital Publishing Institute, vol 3, pp 1–15

Ben Ahmed A, Meyer M, Okuyama Y, Ben Abdallah A (2015a) Efficient router architecture, design and performance exploration for many-core hybrid photonic network-on-chip (2d-phenic). In: 2015 2nd International Conference on Information Science and Control Engineering (ICISCE), pp 202–206. doi:10.1109/ICISCE.2015.52

Ben Ahmed A, Meyer M, Okuyama Y, Ben Abdallah A (2015b) Hybrid photonic noc based on non-blocking photonic switch and light-weight electronic router. In: 2015 IEEE International Conference on Systems, Man and Cybernetics (SMC), pp 56–61

Ben Ahmed A, Okuyama Y, Ben Abdallah A (2015c) Contention-free routing for hybrid photonic mesh-based network-on-chip systems. In: 2015 IEEE 9th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), pp 235–242. doi:10.1109/MCSoC.2015.24

Ben Ahmed A, Okuyama Y, Ben Abdallah A (2015d) Non-blocking electro-optic network-on-chip router for high-throughput and low-power many-core systems. In: 2015 World Congress on Information Technology and Computer Applications Congress (WCITCA), pp 1–7. doi:10.1109/WCITCA.2015.7367068

Bogaerts W, De Heyn P, Van Vaerenbergh T, De Vos K, Kumar Selvaraja S, Claes T, Dumon P, Bienstman P, Van Thourhout D, Baets R (2012) Silicon microring resonators. Laser Photonics Rev 6(1):47–73

Brusberg L, Schroder H, Queisser M, Lang K (2012) Single-mode glass waveguide platform for dwdm chip-to-chip interconnects. In: Electronic Components and Technology Conference (ECTC), IEEE 62nd, pp 1532–1539. doi:10.1109/ECTC.2012.6249039

Chan J, Bergman K (2012) Photonic interconnection network architectures using wavelength-selective spatial routing for chip-scale communications. Optical Communications and Networking, IEEE/OSA J Opt Commun Netw 4(3):189–201

Chan J, Hendry G, Biberman A, Bergman K, Carloni LP (2010) Phoenixsim: A simulator for physical-layer analysis of chip-scale photonic interconnection networks. In: Proceedings of the Conference on Design, Automation and Test in Europe, DATE ’10, Belgium, pp 691–696. http://dl.acm.org/citation.cfm?id=1870926.1871093

Chan J, Hendry G, Bergman K, Carloni L (2011) Physical-layer modeling and system-level design of chip-scale photonic interconnection networks. Computer-Aided Design of Integrated Circuits and Systems. IEEE Trans 30(10):1507–1520

Chittamuru SVR, Pasricha S (2015a) Crosstalk mitigation for high-radix and low-diameter photonic noc architectures. Design Test IEEE 32(3):29–39. doi:10.1109/MDAT.2015.2414417

Chittamuru SVR, Pasricha S (2015b) Improving crosstalk resilience with wavelength spacing in photonic crossbar-based network-on-chip architectures. In: 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAs). IEEE, pp 1–4. doi:10.1109/MWSCAS.2015.7282035

Chu S, Pan W, Sato S, Kaneko T, Little B, Kokubun Y (1999) Wavelength trimming of a microring resonator filter by means of a uv sensitive polymer overlay. Photonics Technol Lett IEEE 11(6):688–690

Cypress (2016) Understanding bit-error-rate hotlink. In: http://www.cypress.com/

Esmaeilzadeh H, Blem E, Amant RS, Sankaralingam K, Burger D (2011) Dark silicon and the end of multicore scaling. In: 2011 38th Annual International Symposium on Computer Architecture (ISCA), pp 365–376

Hendry G, Robinson E, Gleyzer V, Chan J, Carloni L, Bliss N, Bergman K (2010) Circuit-switched memory access in photonic interconnection networks for high-performance embedded computing. In: High Performance Computing, Networking, Storage and Analysis (SC), International Conference for, pp 1–12

Hu ZS, Hung FY, Chen KJ, Chang SJ, Hsieh WK, Liao TY (2013) Improvement in thermal degradation of zno photodetector by embedding silver oxide nanoparticles. Funct Mater Lett 6(01):1350,001

Kahng A, Li B, Peh LS, Samadi K (2012) Orion 2.0: A power-area simulator for interconnection networks. Very Large Scale Integration (VLSI) Systems. IEEE Trans 20(1):191–196

Kaliraj PK (2013) Reliability-performance trade-offs in photonic noc architectures Ph.D. thesis, Rochester Institute of Technology

Kappeler R (2004) Radiation testing of micro photonic components Stagiaire Project Report. ESA/ESTEC. September 29, 2004. Ref. No.: EWP 2263

Koch BR, Fang A, Bowers OCJE (2007) Mode-locked silicon evanescent lasers. Optics Express 18(15):11225–11233

Li H, Fourmigue A, Le Beux S, Letartre X, O’Connor I, Nicolescu G (2015) Thermal aware design method for vcsel-based on-chip optical interconnect. In: Proceedings of the 2015 Design, Automation & Test in Europe Conference & Exhibition. EDA Consortium, San Jose, pp 1120–1125. http://dl.acm.org/citation.cfm?id=2755753.2757072

Li Z, Mohamed M, Chen X, Dudley E, Meng K, Shang L, Mickelson AR, Joseph R, Vachharajani M, Schwartz B et al (2012) Reliability modeling and management of nanophotonic on-chip networks. Very Large Scale Integration (VLSI) Systems, IEEE Trans 20(1):98–111

Loh PK, Hsu WJ (2003) Design of a viable fault-tolerant routing strategy for optical-based grids. In: Guo M, Yang LT (eds) Parallel and Distributed Processing and Applications. Springer, Berlin, pp 112–126

McLaren M, Binkert NL, Davis AL, Florentino M (2014) Energy-efficient and fault-tolerant resonator-based modulation and wavelength division multiplexing systems. US Patent 8,705,972

Meyer M, Ben Ahmed A, Okuyama Y, Ben Abdallah A (2015) Fttdor: Microring fault-resilient optical router for reliable optical network-on-chip systems. In: Embedded Multicore/Many-core Systems-on-Chip (MCSoC), IEEE 9th International Symposium on, pp 227–234. doi:10.1109/MCSoC.2015.17

Mohamed M (2013) Silicon nanophotonics for many-core on-chip networks. Ph.D. thesis, University of Colorado

Nikdast M, Xu J (2014) On the impact of crosstalk noise in optical networks-on-chip. In: Design Automation Conference (DAC) pp 1–2

Nikdast M, Xu J, Wu X, Zhang W, Ye Y, Wang X, Wang Z, Wang Z (2014) Systematic analysis of crosstalk noise in folded-torus-based optical networks-on-chip. Computer-aided design of integrated circuits and systems. IEEE Trans 33(3):437–450

Nitta CJ, Farrens MK, Akella V (2011) Resilient microring resonator based photonic networks. In: Proceedings of the 44th Annual IEEE/ACM International Symposium on Microarchitecture, MICRO-44. ACM, New York, NY, pp 95–104. doi:10.1145/2155620.2155632

Pan Y, Kumar P, Kim J, Memik G, Zhang Y, Choudhary A (2009) Firefly: illuminating future network-on-chip with nanophotonics. In: ACM SIGARCH Computer Architecture News, vol 37, pp 429–440. ACM, New York. doi:10.1145/1555815.1555808

Preston K, Sherwood-Droz N, Levy J, Lipson M (2011) Performance guidelines for wdm interconnects based on silicon microring resonators. In: CLEO: 2011 - Laser Science to Photonic Applications, pp 1–2

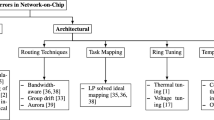

Radetzki M, Feng C, Zhao X, Jantsch A (2013) Methods for fault tolerance in networks-on-chip. ACM Comput Surv 46(1):8

Rafizadeh D, Zhang J, Hagness SC, Taflove A, Stair KA, Ho ST, Tiberio RC (1997) Temperature tuning of microcavity ring and disk resonators at 1.5-mu;m. In: Lasers and Electro-Optics Society Annual Meeting, 1997. LEOS ’97 10th Annual Meeting. Conference Proceedings. IEEE, vol 2, pp 162–163. doi:10.1109/LEOS.1997.645327

Ramesh G, SundaraVadivelu S (2009) A reliable and fault tolerant routing for optical wdm networks. arXiv:0912.0602 (preprint)

Sahasrabuddhe L, Ramamurthy S, Mukherjee B (2002) Fault management in ip-over-wdm networks: Wdm protection versus ip restoration. Selected Areas in Communications. IEEE J 20(1):21–33

Shacham A, Bergman K, Carloni L (2007) On the design of a photonic network-on-chip. In: Networks-on-Chip. NOCS 2007. First International Symposium on, pp 53–64

Shacham A, Bergman K, Carloni L (2008) In: IEEE Transactions on Photonic networks-on-chip for future generations of chip multiprocessors. Comput IEEE Trans 57(9):1246–1260

Tu Z, Zhou Z, Wang X (2014) Reliability considerations of high speed germanium waveguide photodetectors. Proc. SPIE, Optical Components and Materials XI, vol 8982. p 89820W. doi:10.1117/12.2038324

Vantrease D, Schreiber R, Monchiero M, McLaren M, Jouppi NP, Fiorentino M, Davis A, Binkert N, Beausoleil RG, Ahn JH (2008) Corona: System implications of emerging nanophotonic technology. In: Proceedings of the 35th Annual International Symposium on Computer Architecture, ISCA ’08, IEEE Computer Society, Washington pp 153–164. doi:10.1109/ISCA.2008.35

Wolfe J (2012) Why IBM and Intel Are Chasing the 100B Dollar Opportunity in Nanophotonics. http://www.forbes.com/sites/joshwolfe/2012/12/13/why-ibm-and-intel-are-chasing-the-100b-opportunity-in-nanophotonics/. Accessed on 1 July 2015

Xiang D, Zhang Y, Shan S, Xu Y (2013) A fault-tolerant routing algorithm design for on-chip optical networks. In: IEEE 32nd International Symposium on Reliable Distribute Systems, pp 1–9. doi:10.1109/SRDS.2013.9

Xingyun Q, Quanyou F, Yongran C, Qiang D, Wenhua D (2009) A fault tolerant bufferless optical interconnection network. In: Eighth IEEE/ACIS International Conference on Computer and Information Science, pp 249–254. doi:10.1109/ICIS.2009.136

Xu Y, Yang J, Melhem R (2012) Tolerating process variations in nanophotonic on-chip networks. ISCA ’12 Proceedings of the 39th Annual International Symposium on Computer Architecture, IEEE Computer Society Washington, DC, USA, pp 142–152. doi:10.1145/2366231.2337176

Ye Y, Wu X, Xu J, Zhang W, Nikdast M, Wang X (2012) Holistic comparison of optical routers for chip multiprocessors. In: Anti-Counterfeiting, Security and Identification (ASID), pp 1–5. doi:10.1109/ICASID.2012.6325348

Zhang J, Mukheriee B (2004) A review of fault management in wdm mesh networks: basic concepts and research challenges. Netw IEEE 18(2):41–48

Zhu S, Lo GQ (2015) Vertically-stacked multilayer photonics on bulk silicon toward three-dimensional integration. Lightwave Technol J (99):1–1. doi:10.1109/JLT.2015.2499761

Acknowledgments

The authors are grateful to the reviewers who offer us helpful suggestions to improve this paper. This work is partially supported by the University of Aizu Competitive Research funding (CRF), Ref. P-11-2016.

Author information

Authors and Affiliations

Corresponding author

Additional information

This Project is supported by University of Aizu Competitive Research Fund, Ref. P-11-2016.

Rights and permissions

About this article

Cite this article

Meyer, M., Okuyama, Y. & Abdallah, A.B. Microring fault-resilient photonic network-on-chip for reliable high-performance many-core systems. J Supercomput 73, 1567–1599 (2017). https://doi.org/10.1007/s11227-016-1846-0

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-016-1846-0