Abstract

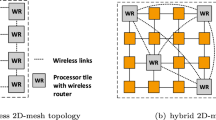

In the current many-core architectures, network-on-chips (NoCs) have been efficiently utilized as communication backbones for enabling massive parallelism and high degree of integration on a chip. In spite of the advantages of conventional NoCs, wired multi-hop links impose limitations on their performance by long delay and much power consumption especially in large systems. To overcome these limitations, different solutions such as using wireless interconnections have been proposed. Utilizing long-range, high bandwidth and low power wireless links can lead to solve the problems corresponding to wired links. Meanwhile, the grid-like mesh is the most stable topology in conventional NoC designs. That is why most of the wireless network-on-chip (WNoC) architectures have been designed based on this topology. The goals of this article are to challenge mesh topology and to demonstrate the efficiency of honeycomb-based WNoC architectures. In this article, we propose HoneyWiN, hybrid wired/wireless NoC architecture with honeycomb topology. Also, a partition-based XYZ-planar routing algorithm for energy conservation is proposed. In order to demonstrate the advantages of the proposed architecture, first, an analytical comparison of HoneyWiN with a mesh-based WNoC, as the baseline architecture, is carried out. In order to compare the proposed architecture, we implement our partition-based routing algorithm in the form of 2-axes coordinate system in the baseline architecture. Simulation results show that HoneyWiN reduces about 17% of energy consumption while increases the throughput by 10% compared to the mesh-based WNoC. Then, HoneyWiN is compared with four state-of-the-art mesh-based NoC architectures. In all of the evaluations, HoneyWiN provides higher performance in term of delay, throughput and energy consumption. Overall, the results indicate that HoneyWiN is very effective in improving throughput, increasing speed and reducing energy consumption.

Similar content being viewed by others

References

Abadal S, Cabellos-Aparicio A, Alarcon E, Torrellas J (2016) WiSync: an architecture for fast synchronization through on-chip wireless communication. In: International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), pp 3–17

Afsharmazayejani R, Yazdanpanah F, Rezaei A, Alaei M, Daneshtalab M (2018) Honeywin: novel honeycomb-based wireless NoC architecture in many-core era. In: 14th International Symposium on Applied Reconfigurable Computing (ARC), Santorini, Greece

Agyeman MO, Vien QT, Ahmadinia A, Yakovlev A, Tong KF, Mak T (2017) A resilient 2-d waveguide communication fabric for hybrid wired-wireless NoC design. IEEE Trans Parallel Distrib Syst 28(2):359–373

Arun M, Jisha P, Jose J (2016) A novel energy efficient multicasting approach for mesh NoCs. Proc Comput Sci Int Conf Adv Comput Commun 93:283–291

Balasubramaniam S, Kangasharju J (2013) Realizing the internet of nano things: challenges, solutions, and applications. Computer 46(2):62–68

Bengio EA, Senic D, Taylor LW, Tsentalovich DE, Chen P, Holloway CL, Babakhani A, Long CJ, Novotny DR, Booth JC, Orloff ND, Pasquali M (2017) High efficiency carbon nanotube thread antennas. Appl Phys Lett 111(16). https://doi.org/10.1063/1.4991822

Benini L, Micheli GD (2002) Networks on chips: a new SoC paradigm. IEEE Comput 35(1):70–78

Binkert NL, Dreslinski RG, Hsu LR, Lim KT, Saidi AG, Reinhardt SK (2006) The M5 simulator: modeling networked systems. IEEE Micro 26(4):52–60

Byeon CW, Yoon CH, Park CS (2013) A 67-mW 10.7-Gb/s 60-GHz OOK CMOS transceiver for short-range wireless communications. IEEE Trans Microw Theory Tech 61(9):3391–3401

Catania V, Mineo A, Monteleone S, Palesi M, Patti D (2015) Noxim: an open, extensible and cycle-accurate network on chip simulator. In: IEEE International Conference on Application-Specific Systems, Architectures and Processors (ASAP), pp 162–163

Catania V, Mineo A, Monteleone S, Palesi M, Patti D (2016) Cycle-accurate network on chip simulation with Noxim. ACM Trans Model Comput Simul 27(1):1–25. https://doi.org/10.1145/2953878

Chang E, Wu A (2017) Overview of high-efficiency ant colony optimization (aco)-based adaptive routings for traffic balancing in network-on-chip systems. In: International Conference on ASIC (ASICON), pp 80–83

Chang MCF, Socher E, Tam SW, Cong J, Reinman G (2008) RF interconnects for communications on-chip. In: International Symposium on Physical Design, ISPD ’08, pp 78–83

Chang MF, Cong J, Kaplan A, Naik M, Reinman G, SoCher E, Tam SW (2008) CMP network-on-chip overlaid with multi-band RF-interconnect. In: International Symposium on High Performance Computer Architecture (HPCA), pp 191–202

Dai J, Jiang X, Watanabe T (2017) An adaptive routing algorithm based on network partitioning for 3D network-on-chip. In: International Conference on Computer, Information and Telecommunication Systems (CITS), pp 229–233

Deb S, Chang K, Cosic M, Ganguly A, Pande PP, Heo D, Belzer B (2012) Cmos compatible many-core NoC architectures with multi-channel millimeter-wave wireless links. In: Great Lakes Symposium on VLSI, GLSVLSI ’12, pp 165–170

Deb S, Chang K, Yu X, Sah SP, Cosic M, Ganguly A, Pande PP, Belzer B, Heo D (2013) Design of an energy-efficient cmos-compatible NoC architecture with millimeter-wave wireless interconnects. IEEE Trans Comput 62(12):2382–2396

Deb S, Ganguly A, Pande PP, Belzer B, Heo D (2012) Wireless NoC as interconnection backbone for multicore chips: promises and challenges. IEEE J Emerg Sel Top Circuits Syst 2(2):228–239

Dehghani A, Jamshidi K (2015) A fault-tolerant hierarchical hybrid mesh-based wireless network-on-chip architecture for multicore platforms. J Supercomput 71(8):3116–3148

DiTomaso D, Kodi A, Kaya S, Matolak D (2011) iwise: inter-router wireless scalable express channels for network-on-chips (NoCs) architecture. In: Annual Symposium on High Performance Interconnects (HOTI), pp 11–18

Duraisamy K, Xue Y, Bogdan P, Pande PP (2017) Multicast-aware high-performance wireless network-on-chip architectures. IEEE Trans Very Large Scale Integr VLSI Syst 25(3):1126–1139

Ebrahimi M, Daneshtalab M, Liljeberg P, Plosila J, Flich J, Tenhunen H (2014) Path-based partitioning methods for 3d networks-on-chip with minimal adaptive routing. IEEE Trans Comput 63(3):718–733

Floyd BA, Guo X, Caserta J, Dickson T, Hung CM, Kim K, Kenneth KO (2002) Wireless interconnects for clock distribution. In: 8th ACM/IEEE International Workshop on Timing Issues in the Specification and Synthesis of Digital Systems, TAU ’02, pp 105–108

Gade SH, Deb S (2017) Hywin: hybrid wireless NoC with sandboxed sub-networks for CPU/GPU architectures. IEEE Trans Comput 66(7):1145–1158

Ganguly A, Chang K, Deb S, Pande PP, Belzer B, Teuscher C (2011) Scalable hybrid wireless network-on-chip architectures for multicore systems. IEEE Trans Comput 60(10):1485–1502

Hanson GW (2005) Fundamental transmitting properties of carbon nanotube antennas. IEEE Trans Antennas Propag 53(11):3426–3435

Hu J, Xu J, Huang M, Wu H (2013) A 25-Gbps 8-ps/mm transmission line based interconnect for on-chip communications in multi-core chips. In: IEEE International Microwave Symposium Digest (IMS), pp 1–4

Ito H, Kimura M, Miyashita K, Ishii T, Okada K, Masu K (2008) A bidirectional- and multi-drop-transmission-line interconnect for multipoint-to-multipoint on-chip communications. IEEE J Solid-State Circuits 43(4):1020–1029

Kahng AB, Li B, Peh LS, Samadi K (2012) ORION 2.0: a power-area simulator for interconnection networks. IEEE Trans Very Large Scale Integr VLSI Syst 20(1):191–196

Karkar A, Al-Dujaily R, Yakovlev A., Tong K, Mak T (2012) Surface wave communication system for on-chip and off-chip interconnects. In: International Workshop on Network on Chip Architectures (NoCArc), pp 11–16

Karkar A, Mak T, Tong KF, Yakovlev A (2016) A survey of emerging interconnects for on-chip efficient multicast and broadcast in many-cores. IEEE Circuits Syst Mag 16(1):58–72

Kawasaki K, Akiyama Y, Komori K, Uno M, Takeuchi H, Itagaki T, Hino Y, Kawasaki Y, Ito K, Hajimiri A (2010) A millimeter-wave intra-connect solution. IEEE J Solid-State Circuits 45(12):2655–2666

Liang Y, Yu H, Zhao J, Yang, W, Wang Y (2015) An energy efficient and low cross-talk CMOS sub-THz I/O with surface-wave modulator and interconnect. In: IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), pp 110–115

Magen N, Kolodny A, Weiser U, Shamir N (2004) Interconnect-power dissipation in a microprocessor. In: International Workshop on System Level Interconnect Prediction, SLIP ’04, pp 7–13

Majumdar A, Dash R, Pangracious V, Turuk AK (2017) An efficient multi-objective thermal aware routing algorithm 3d network-on-chips. In: 2017 International Conference on Electrical and Computing Technologies and Applications (ICECTA), pp 1–4

Mineo A, Palesi M, Ascia G, Catania V (2014) An adaptive transmitting power technique for energy efficient mm-wave wireless NoCs. In: Design, automation and test in Europe (DATE). https://doi.org/10.7873/DATE.2014.284

Mohseni Z, Reshadi M (2018) A deadlock-free routing algorithm for irregular 3d network-on-chips with wireless links. J Supercomput 74(2):953–969

Mondal HK, Gade SH, Shamim MS, Deb S, Ganguly A (2017) Interference-aware wireless network-on-chip architecture using directional antennas. IEEE Trans Multi-Scale Comput Syst 3(3):193–205

More A, Taskin B (2012) A unified design methodology for a hybrid wireless 2-D NoC. In: IEEE International Symposium on Circuits and Systems (ISCAS), pp 640–643

Nakajima K, Maruyama A, Kohtani M, Sugiura T, Otobe E, Lee J, Cho S, Kwak K, Lee J, Yoshimasu T, Fujishima M (2014) 23 Gbps 9.4 pJ/bit 80/100 GHz band CMOS transceiver with on-board antenna for short-range communication. In: IEEE Asian Solid-State Circuits Conference (A-SSCC), pp 173–176

Opoku Agyeman M, Zong W, Yakovlev A, Tong KF, Mak T (2017) Extending the performance of hybrid NoCs beyond the limitations of network heterogeneity. J Low Power Electron Appl. https://doi.org/10.3390/jlpea7020008

Rezaei A, Daneshtalab M, Palesi M, Zhao D (2016) Efficient congestion-aware scheme for wireless on-chip networks. In: 24th Euromicro International Conference on Parallel, Distributed, and Network-Based Processing (PDP), pp 742–749

Rezaei A, Daneshtalab M, Safaei F, Zhao D (2016) Hierarchical approach for hybrid wireless network-on-chip in many-core era. Comput Electr Eng 51(C):225–234. https://doi.org/10.1016/j.compeleceng.2015.10.007

Rezaei A, Daneshtalab M, Zhao D (2017) Cap-w: congestion-aware platform for wireless-based network-on-chip in many-core era. Microprocess Microsyst 52:23–33

Rezaei A, Daneshtalab M, Zhao D, Modarressi M (2016) SAMi: self-aware migration approach for congestion reduction in NoC-based MCSoC. In: IEEE International System-on-Chip Conference (SOCC), pp 145–150

Rezaei A, Zhao D, Daneshtalab M, Zhou H (2017) Multi-objective task mapping approach for wireless NoC in dark silicon age. In: Euro-MICRO International Conference on Parallel, Distributed and Network-Based Processing (PDP), pp 589–592

Saxena S, Manur DS, Shamim MS, Ganguly A (2017) A folded wireless network-on-chip using graphene based thz-band antennas. In: International Conference on Nanoscale Computing and Communication (NaNoCom)

Sikder AI, Kodi AK, Louri A (2016) Reconfigurable optical and wireless (R-OWN) network-on-chip for high performance computing. In: 3rd ACM International Conference on Nanoscale Computing and Communication, NANOCOM’16, pp 25:1–25:6

Stojmenovic I (1997) Honeycomb networks: topological properties and communication algorithms. IEEE Trans Parallel Distrib Syst 8, issue 10(10):1036–1042

Vien QT, Agyeman MO, Le TA, Mak T (2017) On the nanocommunications at THz band in graphene-enabled wireless network-on-chip. Math Probl Eng. https://doi.org/10.1155/2017/9768604

Hu WH, Wang C, Bagherzadeh N (2015) Design and analysis of a mesh-based wireless network-on-chip. J Supercomput 71(8):2830–2846

Wettin P, Kim R, Murray J, Yu X, Pande PP, Ganguly A, Heoamlan D (2014) Design space exploration for wireless nocs incorporating irregular network routing. IEEE Trans Comput Aided Des Integr Circuits Syst 33(11):1732–1745

Wu H, Nan L, Tam SW, Hsieh HH, Jou C, Reinman G, Cong J, Chang MCF (2012) A 60 GHz on-chip RF-interconnect with \(\lambda \)/4 coupler for 5 Gbps bi-directional communication and multi-drop arbitration. In: IEEE Custom Integrated Circuits Conference (CICC), pp 1–4

Xiao Z, Baas B (2013) A hexagonal processor and interconnect topology for many-core architecture with dense on-chip networks. In: IFIP WG 10.5/IEEE International Conference on VLSI-SoC: From Algorithms to Circuits and System-on-Chip Design, pp 125–143. Springer, Berlin Heidelberg

Yang P, Wang Q (2015) Heterogeneous honeycomb-like NoC topology and routing based on communication division. J Future Gener Commun Netw 8:19–26

Yao C, Feng C, Zhang M, Guo W, Zhu S, Wei S (2016) Partitioning methods for multicast in bufferless 3d network on chip. In: Conference Computer Engineering and Technology, pp 13–22

Yin A, Chen N, Liljeberg P, Tenhunen H (2012) Comparison of mesh and honeycomb network-on-chip architectures. In: IEEE Conference on Industrial Electronics and Applications (ICIEA), pp 1716–1720

Yin AW, Xu TC, Liljeberg P, Tenhunen H (2009) Explorations of honeycomb topologies for network-on-chip. In: IFIP International Conference on Network and Parallel Computing (NPC), pp 73–79

Yu X, Baylon J, Wettin P, Heo D, Pande PP, Mirabbasi S (2014) Architecture and design of multichannel millimeter-wave wireless NoC. IEEE Des Test 31(6):19–28

Yu X, Sah SP, Rashtian H, Mirabbasi S, Pande PP, Heo D (2014) A 1.2-pJ/bit 16-Gb/s 60-GHz OOK transmitter in 65-nm CMOS for wireless network-on-chip. IEEE Trans Microw Theory Tech 62, issue 10(10):2357–2369

Zhao D, Wang Y, Wu H, Kikkawa T (2015) I(Re)2-WiNoC: exploring scalable wireless on-chip micronetworks for heterogeneous embedded many-core SoCs. Digital Commun Netw 1(1):45–56

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Yazdanpanah, F., AfsharMazayejani, R., Alaei, M. et al. An energy-efficient partition-based XYZ-planar routing algorithm for a wireless network-on-chip. J Supercomput 75, 837–861 (2019). https://doi.org/10.1007/s11227-018-2617-x

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-018-2617-x