Abstract

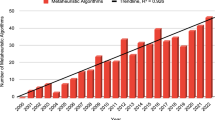

Increasing manufacturing process variations due to aggressive technology scaling in addition to heterogeneity in design components are expected to cause serious challenges for future embedded system design steps including task scheduling. Process variation effects along with increased complexity in embedded applications result in design uncertainties, which in turn, reduce the accuracy and efficiency of traditional design approaches with deterministic values for the design component parameters. In this paper, a multi-objective task scheduling framework is proposed for embedded systems considering uncertainties in both hardware and software component parameters. The tasks which are modeled as a task graph are scheduled on a specific hardware platform consisting of processors and communication parts. Uncertainty is considered in both software (task parameters) and hardware (processor and communication parameters) of the embedded system. UMOTS takes advantages of a Monte-Carlo-based approach within a multi-objective genetic algorithm to handle the uncertainties in model parameters. The proposed approach finds the Pareto frontier, which is robust against uncertainties, in the objective space formed by performance, energy consumption, and reliability. The efficiency of UMOTS is investigated in the experimental results using real-application task graphs. In terms of Scheduling Length Ratio (SLR) and speedup, UMOTS provides 27.8% and 28.6% performance improvements in comparison to HSHD, one state-of-the-art task scheduling algorithm. Additionally, UMOTS, which is based on a multi-objective genetic optimization algorithms, finds robust Pareto frontier with 1%, 5% and 10% uncertainty in design indicators with respect to design limitations.

Similar content being viewed by others

References

Kristina B, Sanja C, Alen J (2021) Systematic review of methodologies for the development of embedded systems. Int J Adv Comput Sci Appl (IJACSA). https://doi.org/10.14569/IJACSA.2021.0120149

Blašković K, Čandrlić S (2018) DEM4RTS: software development methodology for special case of real-time closed-loop control systems. Ann DAAAM & Proc 29

Prongnuch S, Sitjongsataporn S, Wiangtong T (2020) A heuristic approach for scheduling in heterogenous distributed embedded systems. Int J Intell Eng Syst 13(1):135–145

Deng Z, Cao D, Shen H et al (2021) Reliability-aware task scheduling for energy efficiency on heterogeneous multiprocessor systems. J Supercomput. https://doi.org/10.1007/s11227-021-03764-x

Ullman J (1975) NP-complete scheduling problems. J Comput Syst Sci 10(3):384–393

Abdi A, Girault A, Zarandi H (2019) (2019) ERPOT: a quad-criteria scheduling heuristic to optimize execution time, reliability, power consumption and temperature in multicores. IEEE Trans Parallel Distrib Syst 30(10):2193–2210

Lombardi M, Milano M, Benini L (2013) Robust scheduling of task graphs under execution time uncertainty. IEEE Trans Comput 62(1):98–111

Yeh D, Peh L, Borkar S, Darringer J, Agarwal A, Hwu W (2008) Thousand-core chips [roundtable]. IEEE Des Test Comput 25(3):272–278

Yamamoto A, Ababei C (2104) Unified reliability estimation and management of NoC based chip multiprocessors. Microprocessors Microsyst 38(1):53–63

Erbas C, Cerav-Erbas S, Pimentel A (2006) Multiobjective optimization and evolutionary algorithms for the application mapping problem in multiprocessor system-on-chip design. IEEE Trans Evol Comput 10(3):358–374

Kianzad V, Bhattacharyya S (2004) CHARMED: a multi-objective co-synthesis framework for multi-mode embedded systems. 15th IEEE International Conference on Application-Specific Systems, Architectures and Processors. https://doi.org/10.1109/ASAP.2004.1342456

Nedjah N, da Silva M, de Macedo ML (2011) Customized computer-aided application mapping on NoC infrastructure using multi-objective optimization. J Syst Architect 57(1):79–94

Kang S-H, Yang H, Schor L, Bacivarov I, Ha S, Thiele L (2012) Multi-objective mapping optimization vi problem decomposition for many-core systems. 2012 IEEE 10th Symposium on Embedded Systems for Real-time Multimedia, pp 28–37

Ascia G, Catania V, Palesi M (2004) A GA-based design space exploration framework for parameterized system-on-a-chip plathforms. IEEE Trans Evol Comput 8(4):329–346

Balarin F, Watanabe Y, Hsieh H, Lavagno L, Passerone C, Sangiovanni-Vincentelli A (2003) Metropolis: an integrated electronic system design environment”. IEEE Comput 36(4):45–52

Cassidy A, Paul J, Thomas D (2003) Layered, multi-threaded, high-level performace design. 2003 Design Automation and Test in Europe Conference and Exhibition.https://doi.org/10.1109/DATE.2003.1253728

Domer R, Gerstlauer A, Peng J, Shin D, Cai L, Yu H, Abdi S, Gajski D (2008) System-on-chip environment: a Spec C-based framework for heterogeneous MPSo design. EURASIP J Embed Syst. https://doi.org/10.1155/2008/647953

Nikolov H, Stefanov T, Deprettere E (2008) Systematic and automated multiprocessor system design, programming, and implementation. IEEE Trans Comput Aided Des Integr Circuits Syst 27(3):542–555

Pillai A, Singh K, Saravanan V, Anpalagan A, Woungang I, Barolli L (2017) A genetic algorithm-based method for optimizing the energy consumption and performance of multiprocessor systems. Soft Comput 22(10):3271–3285

Zhang J, Zhou D, Yang Y, Lai R, Gao X (2010) Energy optimization of NoC based on voltage-frequency islands under processor reliability constraints. J Electron Inf Technol 33(9):2205–2211

Zhou J, Wei T, Chen M, Hu XS, Ma Y, Zhang G, Yan J (2018) Variation-aware task allocation and scheduling for improving reliability of real-time MPSoCs. In: 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE) (pp 171–176). IEEE

Meedeniya I, Aleti A, Grunske L (2012) Architecture-driven reliability optimization with uncertain model parameters. J Syst Softw 85(10):2340–2355

Guan W, Moghaddam M, Ababei C (2018) Uncertainty aware mapping of embedded systems for reliability, performance, and energy. 2018 19th International Symposium on Quality Electronic Design (ISQED). https://doi.org/10.1109/ISQED.2018.8357284

Bandyszak T, Daun M, Tenbergen B, Kuhs P, Wolf S, Weyer T (2020) Orthogonal uncertainty modeling in the engineering of cyber-physical systems. IEEE Trans Autom Sci Eng 17(3):1250–1265

Li F, Liao TW, Cai W, Zhang L (2020) Multitask scheduling in consideration of fuzzy uncertainty of multiple criteria in service-oriented manufacturing. IEEE Trans Fuzzy Syst 28(11):2759–2771

Muhuri PK, Nath R, Shukla AK (2020) Energy efficient task scheduling for real-time embedded systems in a fuzzy uncertain environment. IEEE Trans Fuzzy Syst

Pimentel A, Erbas C, Polstra S (2006) A systematic approach to exploring embedded system architectures at multiple abstraction levels. IEEE Trans Comput. https://doi.org/10.1109/TC.2006.16

Akbari M, Rashidi H, Alizadeh S (2017) An enhanced genetic algorithm with new operators for task scheduling in heterogeneous computing systems. Eng Appl Artif Intell 61:35–46

Deb K, Agrawal S, Pratap A, Meyarivan T (2002) A fast and elitist multiojective genetic algorithm: NSGA-II. IEEE Trans Evol Comput 6(2):182–197

Das A, Al-Hashimi BM, Merrett GV (2016) Adaptive and hierarchical runtime manager for energy-aware thermal management of embedded systems. ACM Trans Embed Comput Syst (TECS). Embed Comput Syst 15(2):24–34

Sheikh HF, Ahmad I (2016) Sixteen heuristics for joint optimization of performance, energy, and temperature in allocating tasks to multi-cores. ACM Trans Parallel Comput (TOPC). https://doi.org/10.1145/2948973

Abdi A, Zarandi HR (2018) Hystery: a hybrid scheduling and mapping approach to optimize temperature, energy consumption and lifetime reliability of heterogeneous multiprocessor systems. J Supercomput. https://doi.org/10.1007/s11227-018-2248-2

Srinivasan J, Adve S, Bose P, Rivers J (2005) Lifetime reliability: toward an architectural solution. IEEE Micro 25(3):70–80

J. E. D. E. Council, failure mechanisms and models for semiconductor devices, Tech. Rep. JEP122H. 2016, https://www.jedec.org/

Erbas C (2006) System-level modeling and design space exploration for multiprocessor embedded systems-on-chip architectures. Ph.D. thesis, Faculty of Science, Amsterdam University

Embedded System Synthesis Benchmark Suite (E3S) (2008) http://ziyang.eecs.umich.edu/dickrp/e3s/. Accessed 23 Aug 2018

Das A, Kumar A, Veeravalli B, Bolchini C, Miele A, (2014) Combined DVFS and mapping exploration for lifetime and soft-error susceptibility improvement in mpsocs. Proceedings of the Conference on Design, Automation & Test in Europe, pp 61–69

Topcuoglu H, Hariri S, Wu MY (2002) Performance-effective and low-complexity task scheduling for heterogeneous computing. IEEE Trans Parallel Distrib Syst 13(3):260–274

Gupta S, Kumar V, Agarwal G (2010) Task scheduling in multiprocessor system using genetic algorithm. 2010 Second International Conference on Machine Learning and Computing. https://doi.org/10.1109/ICMLC.2010.50

Burkimsher A, Bate I, Indrusiak LS (2013) A survey of scheduling metrics and an improved ordering policy for list schedulers operating on workloads with dependencies and a wide variation in execution times. Future Gener Comput Syst 29:2009–2025

Ijaz S, Munir E, Anwar W, Nasir W (2013) Efficient scheduling strategy for task graphs in heterogeneous computing environment. Int Arab J Inf Technol 10(5):486–492

Kumar V, Katti CP (2014) A scheduling approach with processor and network heterogeneity for grid environment. Int J Comput Sci Eng 6(1):42–48

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix

Appendix

To prove that the genetic operators maintain the order of tasks and would not result in invalid orders, they have to fulfill the following conditions [42]:

-

Correctness following the prioritized dependency of tasks.

-

Competence and uniqueness non-repeated occurrence of all tasks in a given chromosome

Theorem 1

A task orders is an execution order if the tasks keep their dependencies orders. In this case if we remove Ti from the task orders, the remaining tasks still keep the topological order of tasks without violating precedence constrains (Correctness condition).

Proof 1

When \({T}_{i}\) is removed from a topological order, the remaining tasks are actually a topological order of the new graph created by removing \({T}_{i}\) from the original graph. Therefore, all priority constraints of the new graph are preserved in the remaining task orders.

Theorem 2

Task Ti can be inserted into any position among tasks with higher and lower priority then Ti which can provide a new task orders without violating priority constraints; i.e., competence and uniqueness conditions.

Proof 2

All tasks with the same higher and lower priority as Ti are independent of Ti. It means if we change the position of these tasks with each other there is no threat for priority constraints. Hence, the relative order between them in any task orders can be acceptable.

In the following, it is proved that the mutation operator maintains the order of tasks and will not result in invalid orders by fulfilling the necessary conditions [42].

Theorem 3

For mutation, task orders can be replaced in any order without violating priority constraints (Correctness condition).

Proof 3

This is because of the fact that we only replace the tasks in the same segment and the tasks in a segment have the capacity of parallel execution.

Rights and permissions

About this article

Cite this article

Raji, M., Nikseresht, M. UMOTS: an uncertainty-aware multi-objective genetic algorithm-based static task scheduling for heterogeneous embedded systems. J Supercomput 78, 279–314 (2022). https://doi.org/10.1007/s11227-021-03887-1

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-021-03887-1