Abstract

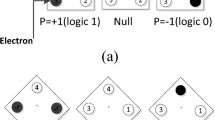

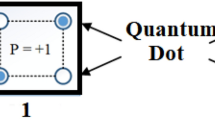

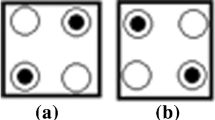

In this manuscript, we first suggest a single-layer 2:1 QCA MUX with an ultra-low number of cells and high speed. Unlike existing designs, the output of the proposed design does not comply with the Boolean regulation and is produced using the essential characteristics of quantum technology. Single-layer 4:1 and 8:1 QCA multiplexers have also been implemented. Moreover, using the proposed 2:1 QCA MUX, a novel and efficient QCA RAM memory cell with the set and reset abilities has been proposed. Forasmuch as the most significant challenge in quantum-dot cellular automata circuit design is the number of cell counts and occupied area. The proposed 2:1 QCA MUX includes 10 cells and an occupied area of 0.03. The unique advantage of the proposed design over all previous output generation tasks is based on cellular interactions. Our findings showed that the proposed 2:1 QCA MUX has a 16.66% and 60% improvement in terms of cell count and occupied area, respectively. In order to confirm the function of the proposed design, some physical proofs are presented. The software for implement of the circuits and their power analysis are QCADesigner 2.0.3 and QCAPro, respectively. The results of the comparisons indicate that the proposed structures are more efficient than the existing ones. The QCAPro power analysis tool has been used for analyzing the power consumption of the proposed designs.

Similar content being viewed by others

References

Bahar AN, Wahid KA (2020) Design of an efficient N × N butterfly switching network in quantum-dot cellular automata (QCA). IEEE Trans Nanotechnol 19:147

Roshany HR, Rezai A (2019) Novel efficient circuit design for multilayer QCA RCA. Int J Theor Phys 58(6):1745–1757

Divshali MN, Rezai A, Hamidpour SSF (2019) Design of novel coplanar counter circuit in quantum dot cellular automata technology. Int J Theor Phys 58(8):2677–2691

Sen B et al (2014) Realizing reversible computing in QCA framework resulting in efficient design of testable ALU. ACM J Emerg Technol Comput Syst 11(3):30

Patidar M, Gupta N (2021) Efficient design and implementation of a robust coplanar crossover and multilayer hybrid full adder–subtractor using QCA technology. J Supercomput. https://doi.org/10.1007/s11227-020-03592-5

Kaity A, Singh S (2021) Optimized area efficient quantum dot cellular automata based reversible code converter circuits: design and energy performance estimation. J Supercomput. https://doi.org/10.1007/s11227-021-03693-9

Foroutan SAH et al (2021) Investigating multiple defects on a new fault-tolerant three-input QCA majority gate. J Supercomput. https://doi.org/10.1007/s11227-020-03567-6

Bahar AN, Wahid KA (2019) Design of QCA-serial parallel multiplier (QSPM) with energy dissipation analysis. IEEE Trans Circuits Syst II Express Briefs 67:1939

De D, Purkayastha T, Chattopadhyay T (2016) Design of QCA based Programmable Logic Array using decoder. Microelectron J 55:92–107

Cocorullo G et al (2016) Design of efficient QCA multiplexers. Int J Circuit Theory Appl 44(3):602–615

Ahmadpour SS, Mosleh M, Rasouli Heikalabad S (2019) Robust QCA full-adders using an efficient fault-tolerant five-input majority gate. Int J Circuit Theory Appl 47:1037

Ahmadpour SS, Mosleh M (2019) A novel ultradense and low-power structure for fault-tolerant three-input majority gate in QCA technology. Concurr Comput Practice Exp. https://doi.org/10.1002/cpe.5548

Kassa SR, Nagaria R, Karthik R (2018) Energy efficient neoteric design of a 3-input majority gate with its implementation and physical proof in quantum dot cellular automata. Nano Commun Netw 15:28–40

Balali M, Rezai A (2018) Design of low-complexity and high-speed coplanar four-bit ripple carry adder in QCA technology. Int J Theor Phys 57(7):1948–1960

Rashidi H, Rezai A (2017) High-performance full adder architecture in quantum-dot cellular automata. J Eng 1(1):394

Wang L, Xie G (2018) Novel designs of full adder in quantum-dot cellular automata technology. J Supercomput 74(9):4798–4816

Abutaleb M (2018) Robust and efficient QCA cell-based nanostructures of elementary reversible logic gates. J Supercomput 74(11):6258–6274

Valinataj M (2017) Novel parity-preserving reversible logic array multipliers. J Supercomput 73(11):4843–4867

Khan MH, Thapliyal H, Munoz-Coreas E (2017) Automatic synthesis of quaternary quantum circuits. J Supercomput 73(5):1733–1759

Jayashree H et al (2016) Ancilla-input and garbage-output optimized design of a reversible quantum integer multiplier. J Supercomput 72(4):1477–1493

Kotiyal S, Thapliyal H, Ranganathan N (2015) Reversible logic based multiplication computing unit using binary tree data structure. J Supercomput 71(7):2668–2693

Fam SR, Navimipour NJ (2019) Design of a loop-based random access memory based on the nanoscale quantum dot cellular automata. Photon Netw Commun 37(1):120–130

Seyedi S, Navimipour NJ (2018) Design and evaluation of a new structure for fault-tolerance full-adder based on quantum-dot cellular automata. Nano Commun Netw 16:1

Jeon J-C (2020) Designing nanotechnology QCA–multiplexer using majority function-based NAND for quantum computing. J Supercomput 77:1–17

Jeon J-C (2020) Low-complexity QCA universal shift register design using multiplexer and D flip-flop based on electronic correlations. J Supercomput 76(8):6438–6452

Sadeghi M, Navi K, Dolatshahi M (2019) Novel efficient full adder and full subtractor designs in quantum cellular automata. J Supercomput 15:1–15

Oskouei SM, Ghaffari A (2019) Designing a new reversible ALU by QCA for reducing occupation area. J Supercomput 75(8):5118–5144

Hashemi S, Azghadi MR, Navi K (2019) Design and analysis of efficient QCA reversible adders. J Supercomput 75(4):2106–2125

Das JC, De D (2019) Novel design of reversible priority encoder in quantum dot cellular automata based on Toffoli gate and Feynman gate. J Supercomput 75(10):6882–6903

Banik S, Roy S, Sen B (2019) Application-dependent testing of FPGA interconnect network. IEEE Trans Very Large Scale Integr Syst 27(10):2296–2304

Bahar AN et al (2017) A novel 3-input XOR function implementation in quantum dot-cellular automata with energy dissipation analysis. Alex Eng J 57:729

Bahar AN, Waheed S (2016) Design and implementation of an efficient single layer five input majority voter gate in quantum-dot cellular automata. SpringerPlus 5(1):1–10

Bahar AN et al (2018) Designing efficient QCA even parity generator circuits with power dissipation analysis. Alex Eng J 57(4):2475–2484

Babaie S, Sadoghifar A, Bahar AN (2018) Design of an efficient multilayer arithmetic logic unit in quantum-dot cellular Automata (QCA). IEEE Trans Circuits Syst II Express Briefs 66(6):963–967

Bahar AN et al (2020) Atomic Silicon Quantum Dot: a new designing paradigm of an atomic logic circuit. IEEE Trans Nanotechnol 19:807

Bahar AN, Wahid KA (2020) Design and implementation of approximate DCT architecture in quantum-dot cellular automata. IEEE Trans Very Large Scale Integr Syst 28(12):2530–2539

Walus K et al (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3(1):26–31

Gudivada AA, Sudha GF (2021) Novel optimized tree-based stack-type architecture for 2 n-bit comparator at nanoscale with energy dissipation analysis. J Supercomput 77(5):4659–4680

Farazkish R, Khodaparast F (2015) Design and characterization of a new fault-tolerant full-adder for quantum-dot cellular automata. Microprocess Microsyst 39(6):426–433

Gadim MR, Navimipour NJ (2018) A new three-level fault tolerance arithmetic and logic unit based on quantum dot cellular automata. Microsyst Technol 24:1–11

Afrooz S, Navimipour NJ (2018) Fault-tolerant Design of a Shift Register at the nanoscale based on quantum-dot cellular automata. Int J Theor Phys 57(9):2598–2614

Seyedi S, Navimipour NJ (2017) An optimized design of full adder based on Nanoscale quantum-dot cellular automata. Optik Int J Light Electron Opt 158:243

Sherizadeh R, Navimipour NJ (2018) Designing a 2-to-4 decoder on nanoscale based on quantum-dot cellular automata for energy dissipation improving. Optik Int J Light Electron Opt 158:477–489

Seyedi S, Navimipour NJ (2018) An optimized three-level Design of Decoder Based on nanoscale quantum-dot cellular automata. Int J Theor Phys 57(7):2022–2033

Seyedi S, Ghanbari A, Navimipour NJ (2019) New Design of a 4-Bit Ripple Carry Adder on a Nano-Scale Quantum-Dot Cellular Automata. Mosc Univ Phys Bull 74(5):494–501

Seyedi S, Darbandi M, Navimipour NJ (2019) Designing an efficient fault tolerance D-latch based on quantum-dot cellular automata nanotechnology. Optik 185:827–837

Teodósio T, Sousa L (2007) QCA-LG: A tool for the automatic layout generation of QCA combinational circuits. In: Norchip, 2007, IEEE

Kim K, Wu K, Karri R (2007) The robust QCA adder designs using composable QCA building blocks. IEEE Trans Comput Aided Des Integr Circuits Syst 26(1):176–183

Mardiris V, et al (2008) Design and simulation of a QCA 2 to 1 multiplexer. In: 12th WSEAS International Conference on Computers, Heraklion, Greece

Asfestani MN, Heikalabad SR (2017) A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Phys B 512:91–99

Song Z et al (2020) An ultra-low cost multilayer RAM in quantum-dot cellular automata. IEEE Trans Circuits Syst II Express Briefs 67(12):3397–3401

Dehkordi MA et al (2011) Novel RAM cell designs based on inherent capabilities of quantum-dot cellular automata. Microelectron J 42(5):701–708

Hashemi S, Navi K (2012) New robust QCA D flip flop and memory structures. Microelectron J 43(12):929–940

Angizi S et al (2015) Design and evaluation of new majority gate-based RAM cell in quantum-dot cellular automata. Microelectron J 46(1):43–51

Asfestani MN, Heikalabad SR (2017) A novel multiplexer-based structure for random access memory cell in quantum-dot cellular automata. Phys B 521:162–167

Ahmadpour S-S, Mosleh M, Asadi M-A (2020) The development of an efficient 2-to-4 decoder in quantum-dot cellular automata. Iran J Sci Technol Trans Electr Eng 45:1–15

Ahmadpour SS, Mosleh M (2020) A novel ultra-dense and low-power structure for fault-tolerant three-input majority gate in QCA technology. Concurr Comput Practice Exp 32(5):e5548

Mardiris VA, Karafyllidis IG (2010) Design and simulation of modular 2n to 1 quantum-dot cellular automata (QCA) multiplexers. Int J Circuit Theory Appl 38(8):771–785

Sen B et al (2012) An efficient multiplexer in quantum-dot cellular automata. Progress in VLSI Design and Test. Springer, pp 350–351

Sen B et al (2014) Modular design of testable reversible ALU by QCA multiplexer with increase in programmability. Microelectron J 45(11):1522–1532

Sen B et al (2015) Towards the hierarchical design of multilayer QCA logic circuit. J Comput Sci 11:233–244

Sen B et al (2015) Towards modular design of reliable quantum-dot cellular automata logic circuit using multiplexers. Comput Electr Eng 45:42–54

Vankamamidi V, Ottavi M, Lombardi F (2008) Two-dimensional schemes for clocking/timing of QCA circuits. IEEE Trans Comput Aided Des Integr Circuits Syst 27(1):34–44

Walus K, et al (2003) RAM design using quantum-dot cellular automata. In: NanoTechnology Conference

Srivastava S, et al (2011) QCAPro-an error-power estimation tool for QCA circuit design. In: 2011 IEEE International Symposium on Circuits and Systems (ISCAS), IEEE

Taskin B, Hong B (2008) Improving line-based QCA memory cell design through dual phase clocking. IEEE Trans Very Large Scale Integr Syst 16(12):1648–1656

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ahmadpour, SS., Mosleh, M. & Rasouli Heikalabad, S. Efficient designs of quantum-dot cellular automata multiplexer and RAM with physical proof along with power analysis. J Supercomput 78, 1672–1695 (2022). https://doi.org/10.1007/s11227-021-03913-2

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-021-03913-2