Abstract

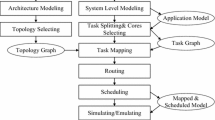

Execution of multiple applications on Multi-Processor System-on-Chips (MPSoCs) significantly boosts performance and energy efficiency. Although various researchers have suggested Network-on-Chip (NoC) architectures for MPSoCs, the problem still needs more investigations for the case of multi-application MPSoCs. In this paper, we propose a fully automated synthesis flow in five steps for the design of custom NoC fabrics for multi-application MPSoCs. The steps include: preprocessing, core to router allocation, voltage island merging, floorplanning, and router to router connection. The proposed flow finds design solutions that satisfy the performance, bandwidth, and power constraints of all input applications. If the user decides, the proposed synthesis adds network-level reconfiguration to improve the efficiency of the obtained design solutions. With the reconfiguration option, the proposed flow comes up with adaptive NoC architectures that satisfy each application’s communication requirements while power-gate idle resources, e.g., router ports and links. If reconfiguration option is not set by the user, the proposed flow considers the top communication requirements among the applications in finding design solutions. We have used the proposed synthesis flow to design custom NoCs for several combined graphs of real-world applications and synthetic graphs. Results show that the reconfiguration option can save up to 98% in the energy-delay product (EDP) of the ultimate designs.

Similar content being viewed by others

Notes

We use the abbreviated terms of Table 1 in this paper.

References

Benini L, De Micheli G (2002) Networks on Chips: a new SoC paradigm, design, automation and test in europe (DATE) conference and exhibition

Kundu S, Chattopadhyay S (2015) Network-on-chip-the next generation of system-on-chip. CRC Press, Boca Raton

Chan J, Parameswaran S (2008) NoCOUT: NoC topology generation with mixed packet-switched and point-to-point networks, Asia and South Pacific Design Automation Conference (ASP-DAC)

Murali S et al (2006) A methodology for mapping multiple use-cases onto networks on chips. Design, Automation & Test in Europe Conference & Exhibition (DATE)

Yang B et al (2013) Mapping multiple applications with unbounded and bounded number of cores on many-core networks-on-chip, Microprocessors and Microsystems (MICPRO)

Zhu D et al (2014) Balancing on-chip network latency in multi-application mapping for chip-multiprocessors. In: IEEE 28th international parallel & distributed processing (PDP)

Upadhyay M et al (2019) Multi-application based network-on-chip design for mesh-of-tree topology using global mapping and reconfigurable architecture. In: International conference on VLSI design (VLSID)

Ali H et al (2019) Energy optimization of streaming applications in IoT on NoC based Heterogeneous MPSoCs using Re-timing and DVFS, IEEE SmartWorld, Ubiquitous Intelligence & Computing

Huang J et al (2018) Reconfigurable topology synthesis for application-specific NoC on partially dynamically reconfigurable systems. Integr VLSI J 65:331–343

Deniziak S, Tomaszewski R (2019) Co-synthesis of contention-free energy-efficient NOC-based real time embedded systems. J Syst Archit 98:92–101

Narayanasamy P et al (2020) Custom NoC topology generation using discrete antlion trapping mechanism. Integr VLSI J 76:76–86

Kashi S et al (2021) An energy efficient synthesis flow for application specific SoC design. Integr VLSI J 81:331–341

Ho WH, Pinkston TM (2003) A methodology for designing efficient on-chip interconnects on well-behaved communication patterns, high-performance computer architecture (HPCA) (2003)

Sahu PK, Chattopadhyay S (2013) A survey on application mapping strategies for Network-on-Chip design. J Syst Archit 59(1):60–76

Kumar N et al (2017) System level fault-tolerance core mapping and FPGA-based verification of NoC. Microelectron J 70:16–26

Khan S et al (2017) Bandwidth-constrained multi-objective segmented brute-force algorithm for efficient mapping of embedded applications on NoC architecture, Data-Driven Monitoring, Fault Diagnosis and Control of Cyber-Physical Systems, Vol. 6 (2017)

Obaidullah M et al (2018) Multi-swarm based NoC configuration and synthesis. In: IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC) (2018)

Gangwar A et al (2020) Automated Synthesis of custom networks-on-chip for real world applications. In: International conference on computer aided design (ICCAD) (2020)

Kumar AS, HanumanthaRao STVK (2021) Computers & Electrical Engineering, 95

Modarressi M et al (2011) Application-aware topology reconfiguration for on-chip networks, IEEE Trans Very Large Scale Integr (TVLSI) Syst 19(11)

Soumya J et al (2014) Multi-application network-on chip design using global mapping and local reconfiguration. ACM Trans Reconfigurable Technol Syst

Mehrvarzy , et al (2016) Power- and performance-efficient cluster-based network-on-chip with reconfigurable topology, Microprocessors and Microsystems (MICPRO)

Wu C et al (2015) An efficient application mapping approach for the co-optimization of reliability, energy, and performance in reconfigurable NoC architectures. IEEE Trans Comput Aided Des Integr Circuits Syst (TCAD) 34(8):1264–1277

Kidane H Leake, Bourennane EB (2018) Run-time reconfigurable network-on-chip: a survey. In: International multi-conference on systems, signals & devices (SSD)

Nguyen HK, Tran X-T (2019) A novel reconfigurable router for QoS guarantees in real-time NoC-based MPSoCs. J Syst Archit 100:101664

Huang J et al (2017) Reconfigurable topology synthesis for application-specific NoC on partially dynamically reconfigurable FPGAs. In: ACM/IEEE international workshop on system level interconnect prediction (SLIP)

Moghaddam MS et al (2017) Optimal mapping of program overlays onto many-core platforms with limited memory capacity. Des Autom Embed Syst 21:173–194

abbaszadeh M et a .(2020) ANDRESTA: an Automated NoC-based design flow for real-time streaming applications. In: CSI/CPSSI international symposium on real-time and embedded systems and technologies (RTEST)

Siast J et al (2019) RingNet: a memory-oriented network-on-chip designed for FPGA. IEEE Trans Very Large Scale Integr (VLSI) Syst 27(6):1284–1297

Kalms L, Göhringer D (2018) Scalable clustering and mapping algorithm for application distribution on heterogeneous and irregular FPGA clusters. J Parallel and Distrib Comput 133:367–376

Hansson A et al (2007) Undisrupted quality-of-service during reconfiguration of multiple applications in networks on chip. In: Design, automation & test in Europe conference & exhibition (DATE)

Sepulveda J et al (2011) A multi-objective approach for multi-application NoC mapping. In: IEEE second Latin American symposium on circuits and systems (LASCAS) (2011)

Li D, Wu J (2016) Energy-efficient contention-aware application mapping and scheduling on NoC-based MPSOCS. J Parallel Distrib Comput 96:1–11

Seiculescu C et al (2009) NoC topology synthesis for supporting shutdown of voltage Islands in SoCs, Design Automation Conference (DAC)

Wang K et al (2017) TSF3D: MSV-driven power optimization for application-specific 3D network-on-chip. IEEE Trans Comput Aided Des Integr Circuits Syst (TCAD) 36(7):1089–1102

Seiculescu C et al (2010) SunFloor 3D: a tool for networks on chip topology synthesis for 3-D systems on chips. IEEE Trans Comput Aided Des Integr Circuits Syst (TCAD) 29(12):1987–2000

Pinto A et al (2003) Efficient synthesis of networks on chip. In: International conference on computer design (ICCD)

Hendrickson B, Leland R (1994) The Chaco user guide: version 2.0, Sandia Tech Report SAND942692

Kapadia N, Pasricha S (2016) A system-level cosynthesis framework for power delivery and on-chip data networks in application-specific 3-D ICs. IEEE Trans VLSI Syst (TVLSI) 24(1):3–16

Adya SN, Markov IL (2003) Fixed-outline floorplanning: enabling hierarchical design. IEEE Trans VLSI Syst (TVLSI) 11(6):1120–1135

Matos D et al (2010) Reconfigurable routers for low power and high performance. IEEE Trans VLSI Syst (TVLSI) 19(11):2045–2057

Tino A, Khan G (2013) High performance NoC synthesis using analytical modeling and simulation with optimal power and minimal IC area. J Syst Archit 59:1348–1363

Kahng A et al (2009) Orion 2.0: a fast and accurate NoC power and area model for early-stage design space exploration. In: Design, automation test in europe conference exhibition (DATE)

Kahng AB et al (2015) ORION3.0: a comprehensive NoC router estimation tool. IEEE Embed Syst Lett 7(2):41–45

Li S et al (2009) McPAT: an integrated power, area, and timing modeling framework for multicore and manycore architectures. In: Annual IEEE/ACM international symposium on microarchitecture (MICRO)

Skadron K et al (2003) Temperature-aware microarchitecture. In: 30th International symposium on computer architecture (ISCA)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kashi, S., Patooghy, A., Rahmati, D. et al. A multi-application approach for synthesizing custom network-on-chips. J Supercomput 78, 15358–15380 (2022). https://doi.org/10.1007/s11227-022-04444-0

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-022-04444-0