Abstract

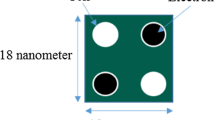

The technological advancements in the semiconductor industry have significantly improved over the years. However, Complementary Metal Oxide Semiconductor (CMOS) technology has its fabrication limitations. This requires new methods and materials for computation at the nanometric level. Quantum-dot cellular automata (QCA) is a revolutionary method that can sidestep CMOS’s practical limits. ALU being the key component in processor design must be optimized for high-speed processing and computation of data to meet the current requirements of portable gadgets. In this paper, a modular approach and extensible architecture for Arithmetic Logic Unit (ALU) design are proposed for high-speed computation. The design of the ALU is extended to perform the computation on multiple bits. The proposed design of the ALU performs 8 operations (four arithmetic, four logical) up to 32-bit computation. The architecture of ALU is made of modular blocks of XOR, XNOR, Adder, and Multiplexer instead of conventional gates. The QCA layout of the 32-bit ALU has 23,189 cells in a 62.68 µm2 area with a delay of 34 clock cycles. The energy dissipation of a 32-bit ALU is 300 meV estimated using coherence vector energy simulation in QCA Designer-E. The delay of an N-bit ALU is calculated by the formula N + 2, which shows the delay efficiency of the proposed architecture of ALU design.

Similar content being viewed by others

Data Availability

Data sharing not applicable to this article as no datasets were generated or analyzed during the current study.

References

RDS Systems and Architectures Team, “International Roadmap for Devices and Systems: Executive Summary,” IEEE Adv. Technol. Humanit., vol. 27, no. 3, pp. 1–63, 2020, [Online]. Available: https://irds.ieee.org/images/files/pdf/2020/2020IRDS_ES.pdf.

Mustafa Badaroglu PAG (2021) System and high-volume-manufacturing more moore scaling roadmap. IEEE Electron Devices Soc Newsletter 28:1–72

Nikonov DE, Young IA (2015) Benchmarking of beyond-cmos exploratory devices for logic integrated circuits. IEEE J Explo Solid-State Comput Devices Circuits 1:3–11

Marković D, Mizrahi A, Querlioz D, Grollier J (2020) Physics for neuromorphic computing. Nat Rev Phys 2(9):499–510. https://doi.org/10.1038/s42254-020-0208-2

Lent CS, Tougaw PD, Porod W, Bernstein GH (1993) Quantum cellular automata. Nanotechnology 4(1):49–57. https://doi.org/10.1088/0957-4484/4/1/004

Timler J, Lent CS (2002) Power gain and dissipation in quantum-dot cellular automata. J Appl Phys 91(2):823–831. https://doi.org/10.1063/1.1421217

Lent CS, Tougaw PD (1997) A device architecture for computing with quantum dots. Proc IEEE 85(4):541–557. https://doi.org/10.1109/5.573740

Sill Torres F et al (2020) On the impact of the synchronization constraint and interconnections in quantum-dot cellular automata. Microprocess. Microsyst 76:103109. https://doi.org/10.1016/j.micpro.2020.103109

Mukhopadhyay D, Dinda S, Dutta P (2011) Designing and implementation of quantum cellular automata 2:1 multiplexer circuit. Int J Comput Appl 25(1):21–24. https://doi.org/10.5120/2996-4026

Tougaw PD, Lent CS (1994) Logical devices implemented using quantum cellular automata. J Appl Phys 75(3):1818–1825. https://doi.org/10.1063/1.356375

Song Z, Xie G, Cheng X, Wang L, Zhang Y (2020) “an ultra-low cost multilayer ram in quantum-dot cellular automata. IEEE Trans Circuits Syst II Express Briefs 67(12):3397–3401. https://doi.org/10.1109/TCSII.2020.2988046

Walus K, Dysart TJ, Jullien GA, Budiman RA (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3(1):26–31. https://doi.org/10.1109/TNANO.2003.820815

Vankamamidi V, Ottavi M, Lombardi F (2008) “Two-dimensional schemes for clocking/timing of QCA circuits”, IEEE Trans. Comput Des Integr Circuits Syst 27(1):34–44. https://doi.org/10.1109/TCAD.2007.907020

Kumari A, Bhanja S (2011) “Landauer clocking for magnetic cellular automata (MCA) arrays”, IEEE Trans. Very Large Scale Integr Syst 19(4):714–717. https://doi.org/10.1109/TVLSI.2009.2036627

Sen B, Nag A, De A, Sikdar BK (2015) Towards the hierarchical design of multilayer QCA logic circuit. J Comput Sci 11:233–244. https://doi.org/10.1016/j.jocs.2015.09.010

Srivastava, S., Asthana, A., Bhanja, S, Sarkar, S. (2011). QCAPro-an error-power estimation tool for QCA circuit design. In 2011 IEEE international symposium of circuits and systems (ISCAS) 2377-2380

Torres FS, Wille R, Niemann P, Drechsler R (2018) An energy-aware model for the logic synthesis of quantum-dot cellular automata. IEEE Trans Comput-Aided Des Integr Circuits Syst 37(12):3031–3041

Ganesh EN (2010) Implementation and simulation of arithmetic logic unit, shifter and multiplier in quantum cellular automata technology. Int J Comput Sci Eng 02(05):1824–1829

Gupta N, Shrivastava S, Patidar N, Katiyal S, Choudhary KK (2012) Design of one bit arithmetic logic unit (ALU) in QCA. Int J Comput Appl Eng Sci 2(3):281–285

Waje MG, Dakhole PK (2013) “Design and implementation of 4-bit arithmetic logic unit using quantum dot cellular automata”, Proc3rd. IEEE Int Adv Comput. Conf. IACC 2013:1022–1029. https://doi.org/10.1109/IAdCC.2013.6514367

Ghosh B, Kumar A, Salimath AK (2014) A simple arithmetic logic unit (12 alu) design using quantum dot cellular automata. Adv Sci Focus 1(4):279–284. https://doi.org/10.1166/asfo.2013.1053

Sen B, Dutta M, Some S, Sikdar BK (2014) realizing reversible computing in Qca framework resulting in efficient design of testable ALU. ACM J Emerg Technol Comput Syst 11(3):1–22. https://doi.org/10.1145/2629538

Goswami M, Sen B, Mukherjee R, Sikdar BK (2017) Design of testable adder in quantum-dot cellular automata with fault secure logic. Microelectron J 60:1–12

Pandiammal K, Meganathan D (2019) “Design of 8 bit reconfigurable ALU using quantum dot cellular automata”, 2018 IEEE 13th nanotechnol. Mater Devices Conf NMDC 2018:1–4. https://doi.org/10.1109/NMDC.2018.8605892

saeed Rasouli Heikalabad MRG (2018) Design of improved arithmetic logic unit in quantum-dot cellular automata. Int J Theor Phys 57:1733–1747. https://doi.org/10.1007/s10773-018-1699-1

Babaie S, Sadoghifar A, Bahar AN (2019) “design of an efficient multilayer arithmetic logic unit in quantum-dot cellular automata (QCA)”,. IEEE Trans Circuits Syst II Express Briefs 66(6):963–967. https://doi.org/10.1109/TCSII.2018.2873797

Bhanja S, Ottavi M, Lombardi F, Pontarelli S (2007) QCA circuits for robust coplanar crossing. J Electron Test 23(2):193–210

Tehrani MA, Bahrami S, Navi K (2014) A novel ternary quantum-dot cell for solving majority voter gate problem. Appl Nanosci 4(3):255–262. https://doi.org/10.1007/s13204-013-0208-y

Liu W, Lu L, Orneill M, Swartzlander EE, Woods R (2011) Design of quantum-dot cellular automata circuits using cut-set retiming. IEEE Trans Nanotechnol 10(5):1150–1160. https://doi.org/10.1109/TNANO.2011.2123915

Zhang M, Yang X, Cui H, Gu Z, Han Z (2021) A design methodology of line feedback shift registers with quantum cellular automata. IEEE Open J Nanotechnol 2:129–139. https://doi.org/10.1109/OJNANO.2021.3129858

Huang J, Momenzadeh M, Schiano L, Lombardi F (2005) “Simulation-based design of modular QCA circuits”, 2005 5th IEEE Conf. Nanotechnol 2(July):721–724. https://doi.org/10.1109/NANO.2005.1500819

Bahar AN, Waheed S, Hossain N, Asaduzzaman M (2018) A novel 3-input XOR function implementation in quantum dot-cellular automata with energy dissipation analysis. Alexandria Eng J 57(2):729–738. https://doi.org/10.1016/j.aej.2017.01.022

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have no conflicts of interest to declare that are relevant to the content of this article.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Patidar, N., Gupta, N. An extensible architecture of 32-bit ALU for high-speed computing in QCA technology. J Supercomput 78, 19605–19627 (2022). https://doi.org/10.1007/s11227-022-04608-y

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-022-04608-y