Abstract

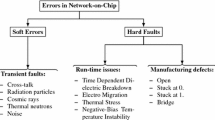

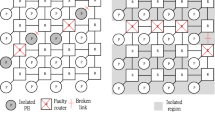

Using of nano-scale Very Large-Scale Integration technologies in Network-on-Chips (NoCs), switches and communication wires of NoCs are sensitive to transient faults. In the architecture of NoCs, switches play an important role in the correct and reliable functions of NoCs against transient faults. The most important transient faults in NoCs are crosstalk faults in wires and Single Event Upset (SEU) and Multipl Event Upset (MBU) faults in buffers. In order to provide reliable switch, we propose a new reconfigurable switch architecture named ReNo to make NoCs more resilience to transient faults. ReNo is able to work in four configurations with several levels of reliability. As a result, local configuration controller logic is used to preserve against transient faults. In ReNo architecture, when a controller finds a high error rate, it configures the switch to a high reliability mode. In this way, imposed performance and power overheads to the switch are minimized. Simulation results which are obtained by Orion patch for power estimation show a significant reliability improvement with a meager performance and power saving at least 20% is achieved in proposed switch architecture, with improvement to state-of-the-art mechanisms.

Similar content being viewed by others

Data Availability Statement

Data can be available by request.

Change history

08 September 2022

A Correction to this paper has been published: https://doi.org/10.1007/s11227-022-04800-0

References

Benini L, De Micheli G (2002) Network on chips: A new SoC paradigm. Computer 35:70–78

Frantz A, Kastensmidt A, Carro F, Cota L (2006) Dependable network-on-chip router able to simultaneously tolerate soft errors and crosstalk. In: Proceedings of the IEEE International Test Conference (ITC), pp 1–9

Dang KN et al (2017) A low-overhead soft–hard fault-tolerant architecture, design and management scheme for reliable high-performance many-core 3D-NoC systems. J Supercomput 73(6):2705–2729

Duan C, Calle VHC, Khatri SP (2009) Efficient on-chip crosstalk avoidance codec design. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol 17, no.4, pp. 551–560, pp. 143–143

Murali S, Theocharides T, Vijaykrishnan N, Irwin MJ, Benini L, De Micheli G (2005) Analysis of error recovery schemes for networks-on-chips. IEEE Des Test Comput 22(5):434–442

Agarwal L, Sylvester K, Blaauw D (2006) Modeling and analysis of crosstalk noise in coupled RLC interconnect. IEEE Trans Comp-Aided Des Integration Circ Syst 25(9):892–901

Ghoneima M, Ismail IY, Khellah MM, Tschanz WJ (2006) Reducing the effective coupling capacitance in buses using threshold voltage adjustment techniques. IEEE Trans Circuits Syst I 53(9):1928–1933

Shirmohammadi Z, Miremadi SG (2015) S2AP: An efficient numerical-based crosstalk avoidance code for reliable data transfer of NoCs. In: Proceedings of the international symposium on reconfigurable communication-centric systems-on-chip (ReCoSoC), pp 1–6, June–July 2015.

Akram BA, Abderazek BA (2016) Adaptive fault-tolerant architecture and routing algorithm for reliable many-core 3D-NoC systems. J Parallel Distributed Comput 93:30–43.

Shi F, Wu X, Yan Z (2012) New crosstalk avoidance codes based on novel pattern classification. In: IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, no. 10, pp. 1892–1902.

Ahmad B, Erdogan AT, Khawam S (2006) Architecture of a dynamically reconfigurable NoC for adaptive reconfigurable MPSoC. In: Proceedings of the First NASA/ESA Conference on Adaptive Hardware and Systems, 2006 AHS, pp.405–411.

Elmiligi H, Morgan AA, El-kharashi MW, Gebali F (2007) Performance Analysis of Networks-on-Chip Routers. In: Proceedings of the International Design and Test workshop, 2007 2nd, 2007, pp. 232–236.

Pionteck T, Albrecht C, Koch R (2006) A dynamically reconfigurable packet-switched network-on-chip. In: Proceedings of the Design Automation & Test inEurope Conference, 2006, pp. 38

Doppa JR et al (2017) Adaptive Manycore Architectures for Big Data Computing. In: Proceedings of the Eleventh IEEE/ACM International Symposium on Networks-on-Chip. ACM, New York

Wang K, Louri A, Karanth A, Bunescu R (2019) High-performance, energy-efficient, fault-tolerant network-on-chip design using reinforcement learning. In: Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Florence, Italy, 2019, pp. 1166–1171.

Sai Manj PD (2017) A scalable network-on-chip microprocessor with 2.5 d integrated memory and accelerator. IEEE Transactions on Circuits and System I: Regular Papers 64.6, pp. 1432–1443.

Véstias, Mário P, Horácio C. Neto (2006) Co-synthesis of a configurable SoC platform based on a network on chip architecture. In: Proceedings of the 2006 Asia and South Pacific Design Automation Conference. IEEE Press, New York.

Kinsy MA et al (2018) SAPA: Self-Aware Polymorphic Architecture. arXiv preprint arXiv:1802.05100.

Shirmohammadi Z, Miremadi SG (2017) An efficient numerical-based crosstalk avoidance codec design for NoCs. Microprocess Microsyst 50:127–137

Shirmohammadi Z, Asadinia M (2020) OnflyTOD: an efficient mechanism for crosstalk fault reduction in WNoC. J Supercomput, Vol. 76

Shirmohammadi Z, Nikoofard AH, Ershadi G (2019) AM3D: an accurate crosstalk probability modeling to predict channel delay in 3D ICs. Microelectronics reliability, Vol.102, November 2019

Bharathi S, Suganthi M, Gowrison G (2020) Crosstalk minimization in network on chip (noc) links with dual binary weighted code codec. J Ambient Intell Humanized Comput, pp 1–6

Frantz APet al (2006) Dependable network-on-chip router able to simultaneously tolerate soft errors and crosstalk. In: 2006 IEEE International Test Conference. IEEE, New York

Eghbal A et al (2010) Designing fault-tolerant network-on-chip router architecture. Int J Electron 97(10):1181–1192

Ebrahimi M, Daneshtalab M, Plosila J, Tenhunen H (2013) MinimalPath Fault-Tolerant Approach Using Connection-Retaining Structure in Networks-on-Chip. In: IEEE/ACM International Symposium on Networks-on-Chip (NOCS), pp. 1–8

Ling Wang, Yadong Wang, Xiaohang Wang (2020) An Approximate Multiplane Network-on-Chip. In: Proceedings of the 23rd Conference on Design, Automation and Test in Europe, pp 234–239

Mercier R, Killian C, Kritikakou A, Helen Y, Chillet D (2021) BiSuT: a NoC-based bit-shuffling technique for multiple permanent mitigation. IEEE Trans. on Comput.-Aided Des. of Integr. Circuit TCAD, 2021, no 21

International Technology Roadmap for Semiconductors, http://public.itrs.net/

Nayebi A et al (2007) “Xmulator: a listener-based integrated simulation platform for interconnection networks. In: Proceedings of the First Asia International Conference on Modelling & Simulation (AMS'07). IEEE, New York, pp. 12–32

Acknowledgements

This work was supported by Shahid Rajaee Teacher University.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

We do not have any COI.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

The original online version of this article was revised: spelling mistake in the name of author Fereshte Mozafari; missing affiliation for Mona Jalal.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Shirmohammadi, Z., Allivand, Y., Mozafari, F. et al. ReNo: novel switch architecture for reliability improvement of NoCs. J Supercomput 79, 2801–2818 (2023). https://doi.org/10.1007/s11227-022-04732-9

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-022-04732-9