Abstract

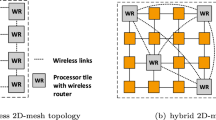

This paper proposes an energy-efficient hybrid Networks-on-Chip architecture called SaHNoC, which is more self adaptive with respect to selection of Wi-Fi positions in a Mesh topology. In comparison with wired on-chip interconnect NoC, wireless interconnect NoC offers a promising performance with respect to communication speed. However, the wireless switch occupies a larger area and has higher power-energy consumption than the wired switch. In this paper, we develop an optimal energy-efficient wire-wireless NoC structure called Hybrid NoC. The proposed hybrid NoC approach explores the self-adaptive technique for the selection of wireless switching positions in a suitable location against topology with respect to network diameter and average hop count. The effectiveness of the proposed SaHNoC is validated with a modified version of Booksim 2.0 in mutual with Orion 3.0.

Similar content being viewed by others

Data availability

All data analyzed during this study are included in this paper.

References

Benini L, De Micheli G (2002) Networks on chips: a new SoC paradigm. IEEE Comput 35(1):70–78

Kumar S, Jantsch A, Soininen JP, Forsell M, Millberg M, Oberg J, Tiensyrja K, Hemani A (2002) A network on chip architecture and design methodology, In: Proc. ISVLSI, pp 117–124

Dally WJ, Towles B (2001) Route packets, not wires: on-chip interconnection networks, In: Proc. DAC, pp 684–689

Pande PP, Grecu C, Jones M, Ivanov A, Saleh R (2005) Performance evaluation and design trade-offs for network-on-chip interconnect architectures. IEEE Trans Comput 54(8):1025–1040

Yu X, Sah SP, Deb S, Pande PP, Belzer B, Deukhyoun H (2011) A wideband body-enabled millimeter-wave transceiver for wireless network-on-chip, In: Proc. IEEE MWSCAS pp 1–4

Dally WJ, Towles B (2004) Principles and Practices of Interconnection Networks, In: Morgan Kaufmann Publishers, San Francisco, CA

Deb S, Ganguly A, Pande PP, Belzer B, Heo D (2012) Wireless NoC as interconnection backbone for multicore chips: promises and challenges. IEEE J Emer Sel Top Circ Syst 2(2):228–239

Deb S, Chang K, Yu X, Sah SP, Cosic M, Ganguly A, Pande PP, Belzer B, Heo D (2013) Design of an energy efficient CMOS compatible NoC architecture with millimeter-wave wireless interconnects. IEEE Trans Comput 62(12):2382–2396

Wang C, Hu WH, Bagherzadeh N (2011) A wireless network-on-chip design for multicore platforms, In: Proceedings of 19th International Euromicro Conference on Parallel, Distributed and Network-Based Processing (PDP), pp 409–416

Lee SB, Tam SW, Pefkianakis I, AL ET (2009) A scalable micro wireless interconnect structure for cmps, In: Proceedings of the 15th Annual International Conference on Mobile Computing and Networking, pp 217–228

Dai P, Chen J, Zaho Y, Lai YH (2015) A study of a wire-wireless hybrid NoC architecture with an energy-proportional multicast scheme for energy efficiency. Comput Electr Eng 45(2):402–416

Rad F, Reshadi M, Khademzadeh A (2020) Flow control and scheduling mechanism to improve network performance in wireless NoC. IET Commun 14(14):2231–2239

Devanathan M, Ranganathan V, Sivakumar P (2020) Congestion-aware wireless network-on-chip for high-speed communication. Automatika 61(1):92–98

Meir A, Moon JW (1975) Relations between packing and covering number of a tree. Pac J Math 67(1):225–233

Slater PJ (1976) R-domination in graphs. J Assoc Comp Mach 23(3):446–450

Lichtenstein D (1982) Planar satisfiability and its uses. SIAM J Comput 11(1):329–343

Davila R, Fast C, Henning MA, Kenter F (2017) Lower bounds on the distance domination number of a graph. Contrib Discrete Math 12(2):446–450

Xiang W, Wang G, Pickering M, Zhang Y (2016) Big video data for light-field-based 3D telemedicine. IEEE Netw 30(3):30–38

Alagarsamy A, Mahilmaran S, Gopalakrishnan L, Ko SB (2022) FRDS: an efficient unique on-Chip interconnection network architecture. Integration 87:90–103

Gkelias A, Dohler M, Friderikos V (1985) Throughput analysis for persistent CSMA systems. IEEE Trans Commun 33(3):627–638

Takagi H, Kleinrock L, Friderikos V, Hamid Aghvami A (2005) Average packet delay of CSMA/CA with finite user population. IEEE Commun Lett 9(3):273–275

Deb S, Chang K, Yu X, Sah SP, Cosic M, Ganguly A et al (2013) Design of an energy efficient CMOS compatible NoC architecture with millimeter-wave wireless interconnects. IEEE Trans Comp 62(12):2382–2396

Jiang N, Balfour J, Becker DU, Towles B, Dally WJ, Michelogiannakis G, Kim J (2013) A detailed and flexible cycle-accurate Network-on-Chip simulator, In: Proc. ISPASS, pp 86–96

Kahng A, Lin B, Nath S (2015) ORION3.0: a comprehensive NoC router estimation tool. IEEE Embed Syst Lett 7(2):41–45

Manuel Malumbres P, Duato J, Torrellas J (2002) An efficient implementation of tree-based multicast routing for distributed shared-memory multiprocessors, In: Proceedings of SPDP’96: 8th IEEE Symposium on Parallel and Distributed Processing. pp 17–22

Masoumeh E et al (2012) Path-based partitioning methods for 3D networks-on-chip with minimal adaptive routing. IEEE Trans Comput 63(3):718–733

Acknowledgements

The first author thanks DST-FIST for funding the lab facility for supporting this research under grant number SR/FST/ET-II/2019/450.

Funding

None.

Author information

Authors and Affiliations

Contributions

A. Alagrasamy—Conceptualization, Methodology, Software, Investigation, Writing—Original Draft, Funding acquisition, Project administration S. Mahilmaran—Methodology, Formal analysis, Writing—Original Draft L. Gopalakrishnan—Software, Resources, Supervision S. B. Ko—Investigation, Resources, Supervision, Project administration.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no competing interests.

Ethical approval and consent to participate

Not applicable.

Consent for publication

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Alagarsamy, A., Mahilmaran, S., Gopalakrishnan, L. et al. SaHNoC: an optimal energy efficient hybrid networks-on-chip architecture. J Supercomput 79, 6538–6559 (2023). https://doi.org/10.1007/s11227-022-04910-9

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-022-04910-9