Abstract

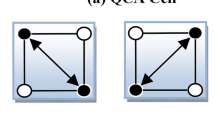

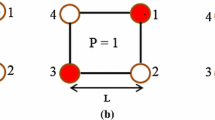

A quantum-dot cellular automaton (QCA) is currently regarded as a radical nanotechnology that is rapidly growing and offering new methods for achieving high-speed computing at the nano-scale. It is an advanced transistor-less nanotechnology, considered for ultra-low-power dissipation, high functioning speed in THz, high device density, and less circuit complexity as a replacement for CMOS technology. This work demonstrates a new circuit design and implementation of the single-bit arithmetic logic unit (ALU) in QCA technology. This can be reduced in terms of the number of quantum cell count, reduced latency, minimization of the design area, optimization of the power consumption and calculation of the effects of temperature on output cell at temperature range 1–7 K by using novel QCADesigner-E (Energy) Version 2.2 tool. The presented ALU design is constructed by 18 × 18 nm QCA cell size, using coherence vector simulation engine setup parameters to provide a regular synchronized clock zone. The proposed design has achieved an improvement of 46.15% of the overall design area, 36.36% of the QCA cell area, and 25.00% of the delay by using the multilayer crossover technique. The proposed design of the QCA–ALU layout and functional verification of the design is performed by using the QCADesigner-E.

Similar content being viewed by others

Explore related subjects

Discover the latest articles and news from researchers in related subjects, suggested using machine learning.Data availability

All data generated or analyzed during this study are included in this published article.

References

Lent CS, Tougaw PD, Porod W (1993) Bistable saturation in coupled quantum dots for quantum cellular automata. Appl Phys Lett 62(7):741–746

Lent CS, Tougaw PD, Porod W, Bernstein GH (1993) Quantum cellular automata. Nanotechnology 4(1):49–57. https://doi.org/10.1088/0957-4484/4/1/004

Kamali SF, Tabrizchi S, Mohammadyan S, Rastgoo M, Navi K (2020) Designing positive, negative and standard gates for ternary logics using quantum dot cellular automata. Comput Electr Eng 83:106590. https://doi.org/10.1016/j.compeleceng.2020.106590

Kumar P, Singh S (2019) Optimization of the area efficiency and robustness of a QCA-based reversible full adder. J Comput Electron 18:1478–1489. https://doi.org/10.1007/s10825-019-01369-5

Retallick J, Walus K (2020) Limits of adiabatic clocking in quantum-dot cellular automata. J Appl Phys 127(5):0545021–0545035. https://doi.org/10.1063/1.5135308

Sabbaghi-Nadooshan R, Kianpour M (2014) A novel QCA implementation of MUX-based universal shift register. J Comput Electron 13:198–210. https://doi.org/10.1007/s10825-013-0500-9

Murotiya SL, Gupta A (2014) Design of CNTFET-based 2-bit ternary ALU for nanoelectronics. Int J Electron 101(9):1244–1257. https://doi.org/10.1080/00207217.2013.828191

Selcuk E (2009) Guided and deterministic self organization of quantum dots. Tech Univ Eindh https://research.tue.nl/en/publications/guided-and-deterministic-self-organization-of-quantum-dots, https://doi.org/10.6100/IR642818.

Singh G, Sarin RK, Raj B (2016) A novel robust exclusive-OR function implementation in QCA nanotechnology with energy dissipation analysis. J Comput Electron 15(2):455–465. https://doi.org/10.1007/s10825-016-0804-7

Ahmadpour SS, Mosleh M, Heikalabad SR (2020) An efficient fault-tolerant arithmetic logic unit using a novel fault-tolerant 5-input majority gate in quantum-dot cellular automata. Comput Electric Eng 82:106548. https://doi.org/10.1016/j.compeleceng.2020.106548

Sangsefidi M, Abedi D, Yoosefi E, Karimpour M (2018) High speed and low cost synchronous counter design in quantum-dot cellular automata. Microelectron J 73:1–11. https://doi.org/10.1016/j.mejo.2017.12.011

Patidar M, Gupta N (2021) Efficient design and implementation of a robust coplanar crossover and multilayer hybrid full adder-subtractor using QCA technology. J Supercomput 77:7893–7915. https://doi.org/10.1007/s11227-020-03592-5

Patidar M, Gupta N (2021) An ultra-efficient design and optimized energy dissipation of reversible computing circuits in QCA technology using zone partitioning method. Int J Inf Tecnol. https://doi.org/10.1007/s41870-021-00775-y

Khan A, Arya R (2021) High performance nanocomparator: a quantum dot cellular automata-based approach. J Supercomput. https://doi.org/10.1007/s11227-021-03961-8

Safaiezadeh B, Mahdipour E, Haghparast M et al (2021) Novel design and simulation of reversible ALU in quantum dot cellular automata. J Supercomput. https://doi.org/10.1007/s11227-021-03860-y

Sen B, Sahu Y, Mukherjee R, Nath RK, Sikdar BK (2016) On the reliability of majority logic structure in quantum-dot cellular automata. Microelectron J 47:7–18. https://doi.org/10.1016/j.mejo.2015.11.002

Bahar AN, Ahmad F, Wani S, Al-Nisa S, Bhat GM (2018) New modified-majority voter-based efficient QCA digital logic design. Int J Electron 106(3):333–348. https://doi.org/10.1080/00207217.2018.1531315

Najafabadi SA, Rezai A, Jahromi KG (2022) Novel circuit design for reversible multilayer ALU in QCA technology. J Comput Electron 21:1451–1460. https://doi.org/10.1007/s10825-022-01949-y

Patidar M, Gupta N (2019) Efficient design and simulation of novel exclusive-OR gate based on nanoelectronics using quantum-dot cellular automata. (Lecture Notes in Electrical Engineering), vol 476, Springer, pp 599–614, https://doi.org/10.1007/978-981-10-8234-4_48

Abutaleb MM (2020) Utilizing charge reconfigurations of quantum-dot cells in building blocks to design nanoelectronic adder circuits. Comput Electr Eng 86(106712):1–16. https://doi.org/10.1016/j.compeleceng.2020.106712

Liu W, Lu L, O’Neill M, Swartzlander EE (2014) A first step toward cost functions for quantum-dot cellular automata designs. IEEE Trans Nanotechnol 13(3):476–487. https://doi.org/10.1109/TNANO.2014.2306754

Patidar M, Gupta N (2020) An efficient design of edge-triggered synchronous memory element using quantum dot cellular automata with optimized energy dissipation. J Comput Electron 19:529–542. https://doi.org/10.1007/s10825-020-01457-x

Sheikhfaal S, Angizi S, Sarmadi S, Moaiyeri MH, Sayedsalehi S (2015) Designing efficient QCA logical circuits with power dissipation analysis. Microelectron J 46(6):462–471. https://doi.org/10.1016/j.mejo.2015.03.016

Goswami M, Sen B, Mukherjee R, Sikdar BK (2017) Design of testable adder in quantum-dot cellular automata with fault secure logic. Microelectron J 60:1–12. https://doi.org/10.1016/j.mejo.2016.11.008

Pandey R, Gupta N, Patidar N (2014) Design and implementation of 16-bit arithmetic logic unit using quantum dot cellular automata (QCA) technique. Int J Eng Res Appl 4(9):10–16

Heikalabad SR, Hosseinzadeh AHN, Hosseinzadeh M, Oladghaffari T (2015) Midpoint memory: a special memory structure for data-oriented models implementation. J Circuits Syst Comput 24(5):1–14. https://doi.org/10.1142/S0218126615500632

Rad SK, Heikalabad SR (2017) Reversible flip-flops in quantum-dot cellular automata. Int J Theor Phys 56(9):2990–3004. https://doi.org/10.1007/s10773-017-3466-8

Ahmadpour SS, Mosleh M, Heikalabad SR (2020) The design and implementation of a robust single-layer QCA ALU using a novel fault-tolerant three-input majority gate. J Supercomput. https://doi.org/10.1007/s11227-020-03249-3

Babaie S, Sadoghifar A, Bahar AN (2019) Design of an efficient multilayer arithmetic logic unit in quantum-dot cellular automata (QCA). IEEE Trans Circuits Syst II Expr Br 66(6):963–967. https://doi.org/10.1109/TCSII.2018.2873797

Antony R, Aravindhan A (2018) Quantum dot cellular automata based arithmetic and logical unit design. Int J Eng Res Technol 7(4):67–72

Pandiammal K, Meganathan D (2018) Design of 8 Bit reconfigurable ALU using quantum dot cellular automata. Paper presented at the IEEE 13th nanotechnology materials and devices conference (NMDC), Portland, OR; 2018, 1–4. https://doi.org/10.1109/NMDC.2018.8605892.

Anitha R, Vijayalakshmi B (2018) Design of 1 bit arithmetic unit in QCA technology using reversible gates. Int J Pure Appl Math 119(15):1041–1045

Tiwari R, Bastawade D, Sharan P, Kumar A (2017) Performance analysis of reversible ALU in QCA. Indian J Sci Technol 10(29):1–5. https://doi.org/10.17485/ijst/2017/v10i29/117324

Sen B, Dutta M, Goswami M, Sikdar BK (2014) Modular design of testable reversible ALU by QCA multiplexer with increase in programmability. Microelectron J 45(11):1522–1532. https://doi.org/10.1016/j.mejo.2014.08.012

Gupta N, Choudhary K, Katiyal S (2013) Two bit arithmetic logic unit (ALU) in QCA. Int J Recent Trends Eng Technol 8(2):35–40

Waje MG, Dakhole PK (2013) Design and implementation of 4-bit arithmetic logic unit using quantum dot cellular automata. Paper presented at the 2013 3rd IEEE international advance computing conference (IACC), Ghaziabad, 2013;1022–1029. https://doi.org/10.1109/IAdCC.2013.6514367

Tahoori MB, Momenzadeh M, Huang J, Lombardi F (2004) Defects and faults in quantum cellular automata at nano scale. Paper presented at the 22nd IEEE VLSI test symposium, 2004, Proceedings, Napa Valley, CA, USA 2004; 291–296. https://doi.org/10.1109/VTEST.2004.1299255

Huang J, Momenzadeh M, Tahoori MB, Lombardi F (2004) Defect characterization for scaling of QCA devices. Paper presented at the 2012 IEEE international symposium on defect and fault tolerance in VLSI and nanotechnology systems (DFT), Cannes, France; 2004, 30–38. https://doi.org/10.1109/DFTVS.2004.1347822

Walus K, Dysart TJ, Jullien GA, Budiman RA (2004) QCADesigner: a rapid design and Simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3:26–31. https://doi.org/10.1109/TNANO.2003.820815

Torres FS, Wille R, Niemann P, Drechsler R (2018) An energy-aware model for the logic synthesis of quantum-dot cellular automata. IEEE Trans Comput Aid Des Integr Circuits Syst 37(12):3031–3041. https://doi.org/10.1109/TCAD.2018.2789782

Kumar D, Mitra D (2016) Design of a practical fault-tolerant adder in QCA. Microelectron J 53:90–104. https://doi.org/10.1016/j.mejo.2016.04.004

Sasamal TN, Singh AK, Mohan A (2020) Quantum-dot cellular automata based digital logic circuits: a design perspective. Springer, Singapore

Abdullah-Al-Shafi M, Bahar AN (2018) An architecture of 2-dimensional 4-dot 2-electron QCA full adder and subtractor with energy dissipation study. Active Passive Electron Compon 2018:1–10. https://doi.org/10.1155/2018/5062960

Mardiris VA, Karafyllidis IG (2010) Design and simulation of modular 2 to 1 quantum-dot cellular automata (QCA) multiplexers. Int J Circuit Theory Appl 38:771–785

Patidar M, Shrivastava A, Miah S, Kumar Y, Sivaraman AK (2022) An energy efficient high-speed quantum-dot based full adder design and parity gate for nano application. Mater Today Proc. https://doi.org/10.1016/j.matpr.2022.03.532

Oskouei SM, Ghaffari A (2019) Designing a new reversible ALU by QCA for reducing occupation area. J Supercomput 75:5118–5144. https://doi.org/10.1007/s11227-019-02788-8

Tiwari A, Patidar M, Jain A, Patidar N, Gupta N (2022) Efficient designs of high-speed combinational circuits and optimal solutions using 45- ° cell orientation in QCA nanotechnology. Mater Today Proc. https://doi.org/10.1016/j.matpr.2022.06.174

Acknowledgements

We wish to thank the anonymous referees for their valuable comments and suggestions that contributed to improving the quality of the work in this paper.

Funding

No research grants from any funding agencies.

Author information

Authors and Affiliations

Contributions

Authors M Patidar, U Singh, and GK Prajapati wrote the main manuscript text, Authors M Patidar, SK Shukla, and N Gupta prepared figures and table, Authors M Patidar and N Gupta design the layout and verified the results, Authors M Patidar, U Singh, SK Shukla and GK Prajapati cross-check the results. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

I declare that the authors have no competing interests.

Consent for publication

Authors are responsible for correctness of the statements provided in the manuscript.

Ethics approval

The manuscript should not be submitted to other journal. The submitted work should be original and should not have been published elsewhere. The results should be presented clearly in manuscript, honestly, and without fabrication, falsification or inappropriate data manipulation.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Patidar, M., Singh, U., Shukla, S.K. et al. An ultra-area-efficient ALU design in QCA technology using synchronized clock zone scheme. J Supercomput 79, 8265–8294 (2023). https://doi.org/10.1007/s11227-022-05012-2

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-022-05012-2