Abstract

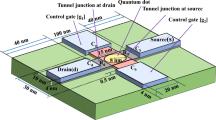

Tunnel field effect transistor (TFET) is a gate-controlled, quantum FET device, exhibiting band-to-band tunneling (BTBT) transport phenomena with lower subthreshold swing (SS) than bulk MOSFET devices. Low ON-state current (ION) is an inherent problem with TFET devices. Various research groups are working to address the limitations due to low ON-state current and for performance improvement of the device. The work in this paper is an attempt to overcome the low switching current issue by using ferroelectric material (Fe), barium titanate (BaTiO3) in conventional double gate TFET, having Si1-xGex/Si semiconductors configuration. In the proposed TFET device, the high-κ dielectric HfO2 is replaced by BaTiO3, ferroelectric material (Fe) in the source region. The replacement of HfO2 gate materials by BaTiO3 Fe is found to improve ION (~ order of 10−8 A/µm -to-10−5 A/µm). The FeDGTFET device shows ~ 103 times improvement in ION with unaffected IOFF (~ 10−20 A/µm). In circuit and system design figure of merit, optimization is a critical task for designers. The work in this paper is divided into three sections. Initially, two structures based on high-κ, one with only high-κ (HfO2) DGTFET and the other one based on HfO2 and ferroelectric material BaTiO3 (FeDGTFET), are compared. Analysis of the electric parameters of the two structures shows the performance advantage of the structure based on the ferroelectric material. Next, a parametric study of the FeDGTFET structure is performed linking Silvaco Atlas with MATLAB to analyze the electrical parameters of FeDGTFET. Finally, an optimization technique called algorithm genetic ‘AG’ is employed to show enhancement in the ION current from 10−5 to 10−4A/µm without affecting the IOFF.

Similar content being viewed by others

Data availability

Original research work.

References

Ilatikhameneh H, Ameen TA, Klimeck G, Appenzeller J, Rahman R (2015) Dielectric engineered tunnel field-effect transistor. IEEE Electron Device Lett 36:1097–1100

Rahi SB, Asthana P, Gupta S (2017) Heterogatejunctionless tunnel field-effect transistor: future of low-power devices. J Comput Electron 16:30–38

Sedighi B, Hu XS, Liu H, Nahas JJ, Niemier M (2015) Analog circuit design using tunnel-FETs. IEEE Trans Circuits Syst I: Regul Papers 62:39–48

Rahi SB, Tayal S, Kumar A (2021) Emerging negative capacitance field effect transistor in low power electronics. Microelectron J 116:105242

Guenifi N, Rahi SB (2022) Low power circuit and system design hierarchy and thermal reliability of tunnel field effect transistor. SILICON 14:3233–3243

Kobayashi M, Jang K, Ueyama N, Hiramoto T (2017) Negative capacitance for boosting tunnel FET performance. IEEE Trans Nanotechnol 16:253–258

Guenifi N, Rahi SB (2021) Design and optimization of heterostructure double gate tunneling field effect transistor for ultra low power circuit and system. Electr Electron Devices Circuits Mater Technol Chall Solut. https://doi.org/10.1002/9781119755104.ch2

Shao Y, del Alamo JA (2022) Sub-10-nm diameter vertical nanowire p-type GaSb/InAsSb tunnel FETs. IEEE Electron Device Lett 43:846–849

Mazumder AAM, Hosen K, Islam MS, Park J (2022) Numerical investigations of nanowire gate-all-around negative capacitance GaAs/InN tunnel FET. IEEE Access 10:30323–30334

Zhao Y, Liang Z, Huang Q, Wang H, Peng Y, Han G, Huang R (2019) Experimental study on the transient response of negative capacitance tunnel FET. In: Electron Devices Technology and Manufacturing Conference (EDTM), pp 88–90

Lee MH, Wei YT, Lin JC, Chen CW, Tu WH, Tang M (2014) Ferroelectric gate tunnel field-effect transistors with low-power steep turn-on. AIP Adv 4:107117

Luk’yanchuk I, Razumnaya A, Sené A, Tikhonov Y, Vinokur VM (2022) The ferroelectric field-effect transistor with negative capacitance. npj Comput Mater 8:1–8

Hu VPH, Lin HH, Lin YK, Hu C (2020) Optimization of negative-capacitance vertical-tunnel FET (NCVT-FET). IEEE Trans Electron Devices 67:2593–2599

Saeidi A, Jazaeri F, Bellando F, Stolichnov I, Luong GV, Zhao QT, Ionescu AM (2017) Negative capacitance as performance booster for tunnel FETs and MOSFETs: an experimental study. IEEE Electron Device Lett 38:1485–1488

Chauhan V, Samajdar DP, Bagga N (2022) Exploration and device optimization of dielectric-ferroelectric sidewall spacer in negative capacitance FinFET. IEEE Trans Electron Devices 69:4717–4724

Lee CC, Hsieh DR, Li SW, Kuo YS, Chao TS (2022) Hysteresis-free gate-all-around stacked poly-Si nanosheet channel ferroelectric HfxZr1-xO2 negative capacitance FETs with internal metal gate and NH3 plasma nitridation. IEEE Trans Electron Devices 69:1512–1518

Kim H, Kwak B, Kim JH, Kwon D (2022) Frequency doubler based on ferroelectric tunnel field-effect transistor. IEEE Trans Electron Devices 69:4046–4049

Verhulst AS, Saeidi A, Stolichnov I, Alian A, Iwai H, Collaert N, Ionescu AM (2020) Experimental details of a steep-slope ferroelectric InGaAs tunnel-FET with high-quality PZT and modeling insights in the transient polarization. IEEE Trans Electron Devices 67:377–382

Elgamal M (2020) A genetic algorithm to optimize the performance of the tunneling field-effect transistor. J Comput Electron 19:1068–1076

Elgamal M (2020) The effect of source and drain pocketing on the performance of double-gate tunnelling field-effect transistor. In: Journal of Physics: Conference Series, IOP Publishing, vol 1447, pp 012020

Hyeok K, Lee M, HyukBae J (2020) Application of genetic algorithm for more efficient multi-layer thickness optimization in solar cells. Energies 13:1726

Basab D, Bhowmick B (2020) Effect of curie temperature on ferroelectric tunnel FET and its RF/analog performance. IEEE Trans Ultrason Ferroelectr Freq Control 68:1437–1441

Tripathi SL, Sinha SK, Patel GS (2020) Low-power efficient p+ Si0. 7Ge0. 3 pocket Junctionless SGTFET with varying operating conditions. J Electron Mater 49:4291–4299

Tripathi SL, Patel GS (2020) Design of low power Si0. 7Ge0. 3 pocket junction-less tunnel FET using below 5 nm technology. Wirel Pers Commun 111:2167–2176

Singh G, Intekhab Amin S, Sunny A, Sarin RK (2016) Design of Si0.5Ge0.5 based tunnel field effect transistor and its performance evaluation. J Superlattices Microstruct 92:143–156

Sahu SA, Goswami R, Mohapatra SK (2020) Characteristic enhancement of hetero dielectric DG TFET using SiGe pocket at source/channel interface: proposal and investigation. SILICON 12:513–520

Ye ZG (eds) (2008) Handbook of dielectric, piezoelectric and ferroelectric materials synthesis, properties and applications. Woodhead Publishing and Maney Publishing on behalf of The Institute of Materials, Minerals & Mining CRC Press Boca Raton Boston New York Washington, DC W OODHEAD PUBLISHING LIMITED Cambridge England First published

Singh KJ, Chauhan N, Bulusu A, Dasgupta S (2022) Physical cause and impact of negative capacitance effect in ferroelectric P (VDF-TrFE) gate stack and its application to landau transistor. IEEE Open J Ultrason Ferroelectr Freq Control 2:55–64

Awadhiya B, Kondekar PN, Meshram AD (2019) Effect of Ferroelectric thickness variation in undoped HfO2-based negative-capacitance field-effect transistor. J Electron Mater. https://doi.org/10.1007/s11664-019-07483-1

Vijatović MM, Bobić JD, Stojanović BD (2008) History and challenges of barium titanate: part II. Sci Sinter 40:235–244. https://doi.org/10.2298/SOS0803235V

Girdhar G, Varma T (2021) Simulation-based analysis of ultra thin-body double gate ferroelectric TFET for an enhanced electric performance, August 5th, 2021, Posted Date: August 5th, 2021, Research Square. https://doi.org/10.21203/rs.3.rs-748137/v1

Guenifi N, Rahi SB, Benmahdi F, Chabane H (2023) Optimization for device figure of merit of ferroelectric tunnel FET using genetic algorithm. ECS J Solid State Sci Technol 12(2):023001

Mitchell M (1998) An introduction to genetic algorithms. MIT press, Cambridge

Albadr MS, Tiun S, Ayob M, Farhad Dhief F (2020) Genetic algorithm based on natural selection theory for optimization problems. Symmetry 12:1758

Acknowledgements

Our research team in this manuscript is thankful to Prof S.C Misra, IIT Kanpur, for kind support and Dr Shiromani Balmukund Rahi acknowledge specially Prof Y. S. Song Department of Computer Science, Korea, for helping.

Funding

None.

Author information

Authors and Affiliations

Contributions

Kindly add all author’s name and their contributions in Authors’ contributions.

Corresponding author

Ethics declarations

Conflict of interest

None.

Ethical approval

The submitted manuscript contains original research work.

Consent to participate

All authors listed in the manuscript have equal contribution from research to manuscript preparation.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Guenifi, N., Rahi, S.B., Benmahdi, F. et al. Optimization of tunneling current in ferroelectric tunnel FET using genetic algorithm. J Supercomput 79, 15773–15789 (2023). https://doi.org/10.1007/s11227-023-05240-0

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-023-05240-0