Abstract

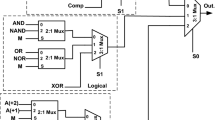

In this paper, a novel high-speed and energy-efficient 4–2 compressor cell is proposed using carbon nanotube field-effect transistors. The proposed compressor is realized efficiently based on NAND–NOR gates and multiplexers. To estimate the performance of the presented design, simulations are carried out using Synopsis HSPICE under different conditions. The results demonstrate the improvement of the proposed design compared to the best reference designs in terms of delay and energy consumption, by 20–26%, respectively. Also, the susceptibility of the proposed design against the process, voltage, temperature (PVT), and noise variations is examined. It is robust against PVT variations and high amplitude of noises compared with its counterpart. Further, embedding the proposed compressor in an 8 × 8-bit binary multiplier demonstrates that it has better speed and energy consumption with regard to its counterparts.

Similar content being viewed by others

Availability of data and materials

Not applicable.

References

Taheri M, Sharifi F, Shafiabadi M, Mahmoodi H, Navi K (2019) Spin-based imprecise 4–2 compressor for energy-efficient multipliers. SPIN 9:1950011

F. Sabetzadeh F, Moaiyeri MH, Ahmadinejad M (2022) An ultra-efficient approximate multiplier with error compensation for error-resilient applications, In: IEEE transactions on circuits and systems II: express briefs

Weinberger A (1981) 4–2 Carry-save adder module. IBM Tech Discl Bull 23:3811–3814

Xiao W, Zhuo C, Qian W (2022) OPACT: optimization of approximate compressor tree for approximate multiplier. 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE) pp 178-183

Safaei Mehrabani Y, Bagherizadeh M, Shafiabadi MH, Ghasempour A (2019) A low-PDAP and high-PSNR approximate 4:2 compressor cell in CNFET technology. Circuit World 45(3):156–168

Masud M, A’ain A, Khan I, Husin N (2019) Design of voltage mode electronically tunable first order all pass filter in ± 0.7 V 16 nm CNFET technology. Electronics 8(1):1–19

Maleknejad M, Mirzaee RF, Navi K, Naji HR (2018) A capacitive multi-threshold threshold gate design to reach a high-performance PVT-tolerant 4:2 compressor by carbon nanotube FETs. Analog Integr Circ Sig Process 94:233–246

Taheri M, Arasteh A, Mohammadyan S, Panahi A, Navi K (2020) A novel majority based imprecise 4:2 compressor with respect to the current and future VLSI industry. Microprocess Microsyst 73:102962

Chang CH, Gu J, Zhang M (2004) Ultra low-voltage low-power CMOS 4–2 and 5–2 compressors for fast arithmetic circuits. IEEE Trans Circuits Syst I Regul Pap 51(10):1985–1997

Bahrepour D, Sharifii MJ (2013) A novel high speed full adder based on linear threshold gate and its application to a 4–2 compressor. Arab J Sci Eng 38:3041–3050

Pishvaie A, Jaberipur G, Jahanian A (2012) Improved CMOS (4; 2) compressor designs for parallel multipliers. Comput Electr Eng 38:1703–1716

Baran D, Aktan M, Oklobdzija VG (2010) Energy efficient implementation of parallel CMOS multipliers with improved compressors. In: Proceedings of the 16th ACM/IEEE international symposium on low power electronics and design 147–152

Pishvaie A, Jaberipur G, Jahanian A (2014) High-performance CMOS (4:2) compressors. Int J Electron 101:1511–1525

Arasteh A, Moaiyeri MH, Taheri M, Navi K, Bagherzadeh N (2018) An energy and area efficient 4:2 compressor based on FinFETs. Integration 60:224–231

Avan A, Maleknejad M, Navi K (2020) High-speed energy efficient process, voltage and temperature tolerant hybrid multi-threshold 4:2 compressor design in CNFET technology. IET Circuits Dev Syst 14:357–368

Rao EJ, Samundiswary P (2022) A systematic comparison of approximate 4–2 compressors for efficient approximate multipliers. In: International Conference on Computing, Communication and Power Technology (IC3P) pp 144–147

Maleknejad M, Mirhosseini SM, Mohammadi S (2021) A CNFET-based PVT-tolerant hybrid majority logic 4:2 compressor design for high speed energy-efficient applications. Microprocess Microsyst. https://doi.org/10.1016/j.micpro.2021.104031

Maleknejad M, Mohammadi S, Mirhosseini SM, Navi K, Naji HR, Hosseinzadeh M (2018) A low-power high-speed hybrid multi-threshold full adder design in CNFET technology. J Comput Electron 17:1257–1267

Jooq MKQ, Moaiyeri MH, Tamersit K (2022) A new design paradigm for auto-nonvolatile ternary srams using ferroelectric CNTFETS: from device to array architecture. IEEE Trans Electron Dev 69(11):6113–6120

R. Zimmermann, Fichtner W (1997) Low-power logic styles: CMOS versus pass-transistor logic. IEEE J Solid-State Circuits 32:1079–1090

Stanford University CNFET Model Website [Online]. Available from: 〈http://nano.stanford.edu/model.php?id=23〉

Deng J, Wong HSP (2007) A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application - Part I: model of the intrinsic channel region. IEEE Trans Electron Dev 54:3186–3194

Deng J, Wong HSP (2007) A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application - Part II: full device model and circuit performance benchmarking. IEEE Trans Electron Dev 57:3186–3194

Emerging Research Devices, n.d. http://www.itrs.net/links/2007ITRS/2007_chapters/2007_ERD.pdf

Weste NHE, Harris D (2010) CMOS VLSI design: a circuits and systems perspective, 4th edn. Addison-Wesley Publishing Company, United States

Li R, Naous R, Fariborzi H, Salama KN (2019) Approximate computing with stochastic transistors’ voltage over-scaling. IEEE Access 7:6373–6385

Sinha SK, Chaudhury S (2013) Impact of temperature variation on CNTFET device characteristics, In: International Conference on Control, Automation, Robotics and Embedded Systems (CARE) pp 1–5

El Shabrawy K, Maharatna K, Bagnall D, Al-Hashimi BM (2010) Modeling SWCNT bandgap and effective mass variation using a monte carlo approach. IEEE Trans Nanotechnol 9(2):184–193

Lin S, Kim Y-B, Lombardi F (2010) Design and analysis of a 32 nm PVT tolerant CMOS SRAM cell for low leakage and high stability. Integr VLSI J 43(2):176–187

Goel S, Kumar A, Bayoumi M (2006) Design of robust, energy-efficient full adders for deep-submicrometer design using hybrid-CMOS logic style. IEEE Trans Very Large Scale Integr (VLSI) Syst 14(12):1309–1321

Funding

This research received no external funding.

Author information

Authors and Affiliations

Contributions

MM analyzed conceptualization, FS performed formal analysis, MM provided project administration, HS developed software, and MM, FS, and HS prepared writing—review and editing. All authors have read and agreed to the published version of the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no conflict of interest.

Ethical approval

All authors have read the Springer journal policies and submit this manuscript in accordance with those policies.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Maleknejad, M., Sharifi, F. & Sharifi, H. A fast and energy-efficient hybrid 4–2 compressor for multiplication in nanotechnology. J Supercomput 80, 11066–11088 (2024). https://doi.org/10.1007/s11227-023-05857-1

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-023-05857-1