Abstract

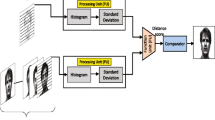

The visual system is essential as a critical source for intelligent robots to acquire external information. Nevertheless, the real-time performance of existing approaches remains inadequate. To address this, a new high-performance target classification system based on FPGA has been developed as part of the visual system. This system optimizes the hardware architecture of the target classification algorithm, incorporating a novel method aimed at boosting parallelism to improve real-time performance. The system is implemented on the Xilinx Zynq-7045 FPGA. Experimental results demonstrate that, for a grayscale image with a resolution of 128 \(\times\) 128, the feature extraction time is merely 85.64 µs, achieving a speed three orders of magnitude greater than that of the MATLAB platform. Additionally, the resource consumption of this design is lower than that of existing hardware architectures.

Similar content being viewed by others

References

Liu L, Long Y, Fieguth PW, Lao S, Zhao G (2014) Brint: binary rotation invariant and noise tolerant texture classification. IEEE Trans Image Process 23(7):3071–3084

Ojala T, Pietikäinen M, Harwood D (1996) A comparative study of texture measures with classification based on featured distributions. Pattern Recogn 29(1):51–59

Guo Z, Zhang L, Zhang D (2010) A completed modeling of local binary pattern operator for texture classification. IEEE Trans Image process 19(6):1657–1663

Guo Z, Wang X, Zhou J, You J (2015) Robust texture image representation by scale selective local binary patterns. IEEE Trans Image Process 25(2):687–699

Liu L, Lao S, Fieguth PW, Guo Y, Wang X, Pietikäinen M (2016) Median robust extended local binary pattern for texture classification. IEEE Trans Image Process 25(3):1368–1381

Xie T, Peng Y, Wang C (2016) hi-rf: incremental learning random forest for large-scale multi-class data classification. arXiv preprint arXiv:1608.08761

Wang J, Yang D, Jiang W, Zhou J (2017) Semisupervised incremental support vector machine learning based on neighborhood Kernel estimation. IEEE Trans Syst Man Cybern Syst 47(10):2677–2687

Cheng W-Y, Juang C-F (2013) A fuzzy model with online incremental SVM and margin-selective gradient descent learning for classification problems. IEEE Trans Fuzzy Syst 22(2):324–337

Diehl CP, Cauwenberghs G ( 2003) SVM incremental learning, adaptation and optimization. In: Proceedings of the International Joint Conference on Neural Networks, 4, pp. 2685– 2690 . IEEE

Kyrkou C, Bouganis C-S, Theocharides T, Polycarpou MM (2015) Embedded hardware-efficient real-time classification with cascade support vector machines. IEEE Trans Neural Netw Learn Syst 27(1):99–112

Zhang Y, Cao W, Wang L ( 2015) Implementation of high performance hardware architecture of face recognition algorithm based on local binary pattern on FPGA. In: 2015 IEEE 11th International Conference on ASIC (ASICON), pp. 1– 4 . IEEE

Kryjak T, Komorkiewicz M, Gorgon M (2012) FPGA implementation of real-time head-shoulder detection using local binary patterns, svm and foreground object detection. In: Proceedings of the 2012 Conference on Design and Architectures for Signal and Image Processing, pp. 1– 8

Kyrkou C, Theocharides T (2009) Scope: towards a systolic array for SVM object detection. IEEE Embed Syst Lett 1(2):46–49

Kyrkou C, Theocharides T (2012) A parallel hardware architecture for real-time object detection with support vector machines. IEEE Trans Comput 61(6):831–842

Koide T, Hoang A-T, Okamoto T, Shigemi S, Mishima T, Tamaki T, Raytchev B, Kaneda K, Kominami Y, Miyaki R, Matsuo T, Yoshida S, Tanaka S ( 2014) FPGA implementation of type identifier for colorectal endoscopie images with NBI magnification. In: 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 651– 654

Shigemi S, Mishima T, Hoang A-T, Koide T, Tamaki T, Raytchev B, Kaneda K, Kominami Y, Miyaki R, Matsuo T, Yoshida S, Tanaka S ( 2013) Customizable hardware architecture of support vector machine in cad system for colorectal endoscopic images with NBI magnification

Ago Y, Nakano K, Ito Y ( 2013) A classification processor for a support vector machine with embedded dsp slices and block rams in the FPGA. In: 2013 IEEE 7th International Symposium on Embedded Multicore Socs, pp. 91– 96

Liu C, Qiao F, Yang X, Yang H (2014) Hardware acceleration with pipelined adder for support vector machine classifier. In: 2014 Fourth International Conference on Digital Information and Communication Technology and its Applications (DICTAP), pp. 13– 16

Papadonikolakis M, Bouganis C-S (2010) A novel FPGA-based SVM classifier. In: 2010 International Conference on Field-Programmable Technology, pp. 283– 286

Papadonikolakis M, Bouganis C-S (2012) Novel cascade FPGA accelerator for support vector machines classification. IEEE Trans Neural Netw Learn Syst 23(7):1040–1052

Patil RA, Gupta G, Sahula V, Mandal AS (2012) Power aware hardware prototyping of multiclass svm classifier through reconfiguration. In: 2012 25th International Conference on VLSI Design, pp. 62– 67 . IEEE

Younes H, Ibrahim A, Rizk M, Valle M (2021) Algorithmic-level approximate tensorial SVM using high-level synthesis on FPGA. Electronics 10(2):205

Ramadurgam S, Perera DG (2021) An efficient FPGA-based hardware accelerator for convex optimization-based SVM classifier for machine learning on embedded platforms. Electronics 10(11)

Afifi S, GholamHosseini H, Sinha R (2018) Dynamic hardware system for cascade SVM classification of melanoma. Neural Comput Appl 32(6):1777–1788

Batista GC, Oliveira DL, Saotome O, Silva WLS (2020) A low-power asynchronous hardware implementation of a novel SVM classifier, with an application in a speech recognition system. Microelectron J 105:104907

Shanmugam S, Dharmar S (2024) Implementation of a non-linear SVM classification for seizure EEG signal analysis on FPGA. Eng Appl Artif Intell 131:107826

Shao S, Mencer O, Luk W ( 2016) Dataflow design for optimal incremental svm training. In: 2016 International Conference on Field-Programmable Technology (FPT), pp. 197– 200 . IEEE

Yang K, Wei M, Sun L ( 2018) Design of median filtering system based on fpga for large windows. In: 2018 IEEE 3rd Advanced Information Technology, Electronic and Automation Control Conference (IAEAC), pp. 78– 82 . IEEE

Kolte P, Smith R, Su W ( 1999) A fast median filter using altivec. In: Proceedings 1999 IEEE International Conference on Computer Design: VLSI in Computers and Processors (Cat. No.99CB37040), pp. 384– 391

Chang C-C, Lin C-J (2011) Libsvm: a library for support vector machines. ACM Trans Intell Syst Technol (TIST) 2(3):1–27

Diehl CP, Cauwenberghs G (2003) Svm incremental learning, adaptation and optimization. In: Proceedings of the International Joint Conference on Neural Networks, 2003., pp. 2685– 26904 . IEEE

Stekas N, Van Den Heuvel D (2016) Face recognition using local binary patterns histograms (lbph) on an fpga-based system on chip (soc). In: 2016 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), pp. 300– 304 . IEEE

Acknowledgement

This project is founded by STI 2030—Major Projects 2022ZD0208700.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Zhang, Y., Guo, X., Guo, H. et al. A new hardware architecture of high-performance real-time texture classification system based on FPGA. J Supercomput 81, 344 (2025). https://doi.org/10.1007/s11227-024-06705-6

Accepted:

Published:

DOI: https://doi.org/10.1007/s11227-024-06705-6