Abstract

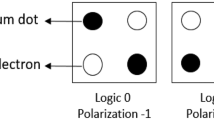

The Quantum-Dot Cellular Automata (QCA) is an incipient nanotechnology in contrast to the CMOS technology with appealing features like low power consumption, high speed and reduced size in implementing the architecture for the computations. QCA provides better and well-organised solution with a modern and exclusive result in performing logical computations at Nano-scale. In this paper mainly focused on design and implementation of 8 \(\times \) 8 Vedic multiplier with the help of 4 \(\times \) 4 Vedic multiplier using Nikhilam and Anurupayan Sutra. The simulation results achieved with the help of QCA Designer tool shows that the area and delay of the proposed 8 \(\times \) 8 Vedic multiplier is decreased by an average of 45.8% and 72.6%, 82.5% and 80.7%, and 17.24% and 21% respectively when compared to 8 \(\times \) 8 Array multiplier, 8 \(\times \) 8 Wallace multiplier, and 8 \(\times \) 8 Urdhva Tiryagbhyam Vedic multiplier. Furthermore, the proposed multiplier is implemented on Kintex-7 (KC705) FPGA board. The results revealed a reduction in area and delay compared to a well-known prior art multipliers.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.References

Kummamuru, R. K., Orlov, A. O., Ramasubramaniam, R., Lent, C. S., Bernstein, G. H., & Snider, G. L. (2003). Operation of a quantum-dot cellular automata (QCA) shift register and analysis of errors. IEEE Transactions on Electron Devices, 50(9), 1906–1913.

Rairigh, D. (2005). Limits of CMOS technology scaling and technologies beyond-CMOS. Piscataway: Institute of Electrical and Electronics Engineers.

Porod, W. (1997). Quantum-dot devices and quantum-dot cellular automata. Journal of the Franklin Institute, 334(5), 1147–1175.

Zhang, R., Walus, K., Wang, W., & Jullien, G. A. (2005). Performance comparison of quantum-dot cellular automata adders. In IEEE International symposium on circuits and systems.

Gavali, K. R, & Kadam, P. (2016). VLSI design of high speed Vedic multiplier for FPGA implementation. In IEEE international conference on engineering and technology (ICETECH).

Cho, H., & Swartzlander, E. E. (2007). Adder designs and analyses for quantum-dot cellular automata. IEEE Transactions on Nanotechnology, 6(3), 374–383.

Cho, H., & Swartzlander, E. E. (2009). Adder and multiplier design in quantum-dot cellular automata. IEEE Transactions on Computers, 58(6), 721–727.

Anjana, S., Pradeep, C. & Samuel, P. (2014). Synthesize of high speed floating-point multipliers based on vedic mathematics. In International conference on information and communication technologies.

Naregal, K., Hebbar, P. K., & Chandu, Y. (2017). Design and implementation of high efficiency vedic binary multiplier circuit based on squaring circuits. In IEEE international conference on recent trends in electronics information & communication technology (RTEICT).

Mistri, N. R., Somani, S. B., & Shete, V. V. (2016). Design and comparison of multiplier using vedic mathematics. In IEEE international conference on inventive computation technologies (ICICT).

Dwivedi, S. P. (2013). An efficient multiplication algorithm using Nikhilam method. In IEEE fifth international conference on advances in recent technologies in communication and computing.

Bansal, Y., Madhu, C., & Kaur, P. (2014). High speed vedic multiplier designs. In IEEE recent advances in engineering and computational sciences (RAECS).

Ram, G. C., Rani, D. S., Balasaikesava, R., & Sindhuri, K. B. (2016). Design of delay efficient modified 16 bit wallace multiplier. In IEEE international conference on recent trends in electronics, information & communication technology.

Hassan, S. Z. (2017). Design and simulation of enhanced 64-bit vedic multiplier. In IEEE Jordan conference on applied electrical engineering and computing technologies (AEECT).

Chudasama, A., & NathSasamal, T. (2016). Implementation of 4 \(\times \) 4 vedic multiplier using carry save adder in quantum-dot cellular automata. In IEEE international conference on communication and signal processing.

Ram, G. C., Rani, D. S., Balasaikesava, R., & Sindhuri, K. B. (2016). VLSI architecture for delay efficient 32-bit multiplier using vedic mathematic sutras. In IEEE international conference on recent trends in electronics, information & communication technology (RTEICT).

Kim, K., Wu, K., & Karri, R. (2007). The robust QCA adder designs using composable QCA building blocks. In IEEE transactions on computer-aided design of integrated circuits and systems Vol. 26, No. 1.

Kim, S.-W., & Earl, E. (2009). Parallel multipliers for quantum-dot cellular automata. In IEEE conference on nanotechnology materials and devices.

Chudasama, A., Sasamal, T. N., & Yadav, J. (2018). An efficient design of Vedic multiplier using ripple carry adder in quantum-dot cellular automata. Computers and Electrical Engineering, 65, 527–542.

Reddy, B. N. K. (2019). Design and implementation of high performance and area efficient square architecture using Vedic mathematics. In Analog integrated circuits and signal processing.

QCA Designer tool version 2.0.3. : https://qcadesigner.soft112.com/.

http://www.xilinx.com/products/boards-and-kits/ek-k7-kc705-g.html.

Beechu, N. K. R., et al. (2017). System level fault-tolerance core mapping and FPGA-based verification of NoC. Microelectronics Journal, 70, 16–26.

Beechu, N. K. R., et al. (2018). Hardware implementation of fault tolerance NoC core mapping. Telecommunication Systems, 68(4), 621–630.

Beechu, N. K. R., et al. (2017). High-performance and energy-efficient fault-tolerance core mapping in NoC. Sustainable Computing: Informatics and Systems, 16, 1–10.

Reddy, B. N. K., Suresh, N., Ramesh, J. V. N., Pavithra, T., Bahulya, Y. K., Edavoor, P. J., Ram, S. J. (2015). An effiient approach for design and testing of FPGA programming using LabVIEW. In International conference on advanced computing, networking and informatics: ICACNI.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Reddy, B.N.K., Vani, B.V. & Lahari, G.B. An efficient design and implementation of Vedic multiplier in quantum-dot cellular automata. Telecommun Syst 74, 487–496 (2020). https://doi.org/10.1007/s11235-020-00669-7

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11235-020-00669-7