Abstract

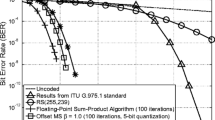

Low Density Parity-Check (LDPC) codes achieve the best performance when they are decoded with the sum-product (SP) algorithm. This is a two-phase iterative algorithm where two types of messages are interchanged and updated in each iteration. The group-shuffled or layered decoding schemes applied to the SP algorithm speed up its convergence by modifying its schedule, so they yield a reduction in the number of iterations required to achieve a given performance. However, the two-phase processing is still maintained. In this paper a modification of the group-shuffled scheme suitable for high-rate LDPC codes is proposed. The modification allows the overlapping of the two-phase computation, achieving a convergence speed up close to that of the group-shuffled scheme with higher throughput. Besides, high throughput architectures are presented for the modified algorithm. As an example, the proposed architecture has been implemented for the 2048-bit LDPC code of the IEEE 802.3an standard and it was synthesized in a 90 nm CMOS process achieving a throughput of 22.40 Gbps at 14 iterations with a clock frequency of 306 MHz and a total area of 10.5 mm2. Furthermore, the decoder performs within 0.5 dB of the floating-point 100 iterations sum-product algorithm at a PER of 10−5.

Similar content being viewed by others

References

IEEE draft standard for information technology—telecommunications and information exchange between systems—local and metropolitan area networks—specific requirements—part 3: Carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specifications (revision of IEEE std 802.3-2005 including all approved amendments) (2008). IEEE Unapproved Draft Std P802.3/D2.2.

Digital Video Broadcasting (DVB) (2009). Second generation framing structure, channel coding and modulation systems for broadcasting, interactive services, news gathering and other broadband satellite applications (DVB-S2). ETSI EN 302 307 V1.2.1

IEEE standard for information technology—telecommunications and information exchange between systems—local and metropolitan area networks—specific requirements. part 15.3: Wireless medium access control (MAC) and physical layer (PHY) specifications for high rate wireless personal area networks (WPANs) amendment 2: Millimeter-wave-based alternative physical layer extension (2009). IEEE Std 802.15.3c-2009.

IEEE standard for information technology—telecommunications and information exchange between systems—local and metropolitan area networks—specific requirements part 11: Wireless LAN medium access control (MAC) and physical layer (PHY) specifications amendment 5: Enhancements for higher throughput. (2009). IEEE Std 802.11n-2009.

IEEE standard for local and metropolitan area networks part 16: Air interface for broadband wireless access systems (2009). IEEE Std 802.16-2009.

Angarita, F., Sansaloni, T., Canet, M., & Valls, J. (2011). Improved sliced message passing architecture for high throughput decoding of LDPC codes. Journal of Signal Processing Systems. doi:10.1007/s11265-011-0580-3.

Blanksby, A., & Howland, C. (2002). A 690-mW 1-Gb/s 1024-b, rate-1/2 low-density parity-check code decoder. IEEE Journal of Solid-State Circuits, 37(3), 404–412.

Darabiha, A., Chan Carusone, A., & Kschischang, F. (2008). Power reduction techniques for LDPC decoders. IEEE Journal of Solid-State Circuits, 43(8), 1835–1845.

Djurdjevic, I., Xu, J., Abdel-Ghaffar, K., & Lin, S. (2003). A class of low-density parity-check codes constructed based on reed-solomon codes with two information symbols. IEEE Communications Letters, 7(7), 317–319.

Fossorier, M. (2004). Quasicyclic low-density parity-check codes from circulant permutation matrices. IEEE Transactions on Information Theory, 50(8), 1788–1793.

Gallager, R. (1962). Low-density parity-check codes. IRE Transactions on Information Theory, 8(1), 21–28.

Jin, J., & ying Tsui, C. (2010). An energy efficient layered decoding architecture for LDPC decoder. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 18(8), 1185–1195.

Kschischang, F., Frey, B., & Loeliger, H.A. (2001). Factor graphs and the sum-product algorithm. IEEE Transactions on Information Theory, 47(2), 498–519.

Liu, L., & Shi, C.J. (2008). Sliced message passing: High throughput overlapped decoding of high-rate low-density parity-check codes. IEEE Transactions on Circuits and Systems I: Regular Papers, 55(11), 3697–3710.

Lu, J., & Moura, J. (2006). Structured LDPC codes for high-density recording: Large girth and low error floor. IEEE Transactions on Magnetics, 42(2), 208–213.

MacKay, D. (1999). Good error-correcting codes based on very sparse matrices. IEEE Transactions on Information Theory, 45(2), 399–431.

Mohsenin, T., & Baas, B.M. (2010). A split-decoding message passing algorithm for low density parity check decoders. Journal of Signal Processing Systems, 61(3), 329–345.

Oh, D., & Parhi, K. (2009). Low complexity decoder architecture for low-density parity-check codes. Journal of Signal Processing Systems, 56(2–3), 217–228.

Richardson, T., & Urbanke, R. (2001). The capacity of low-density parity-check codes under message-passing decoding. IEEE Transactions on Information Theory, 47(2), 599–618.

Sha, J., Lin, J., Wang, Z., Li, L., & Gao, M. (2009). Decoder design for RS-based LDPC codes. IEEE Transactions on Circuits and Systems II: Express Briefs, 56(9), 724–728.

Sharon, E., Litsyn, S., & Goldberger, J. (2007). Efficient serial message-passing schedules for LDPC decoding. IEEE Transactions on Information Theory, 53(11), 4076–4091.

Sun, Y., & Cavallaro, J. (2008). A low-power 1-Gbps reconfigurable LDPC decoder design for multiple 4G wireless standards. In 2008 IEEE international SOC conference (pp. 367–370).

Tanner, R. (1981). A recursive approach to low complexity codes. IEEE Transactions on Information Theory, 27(5), 533–547.

Wang, Z., & Cui, Z. (2007). Low-complexity high-speed decoder design for quasi-cyclic LDPC codes. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 15(1), 104–114.

Zhang, J., & Fossorier, M. (2005). Shuffled iterative decoding. IEEE Transactions on Communications, 53(2), 209–213.

Zhang, T., & Parhi, K. (2001). VLSI implementation-oriented (3,k)-regular low-density parity-check codes. In 2001 IEEE workshop on signal processing systems (pp. 25–36).

Zhang, Z., Anantharam, V., Wainwright, M., & Nikolic, B. (2010). An efficient 10Gbase-T ethernet LDPC decoder design with low error floors. IEEE Journal of Solid-State Circuits, 45(4), 843–855.

Acknowledgements

This research was supported by Fondo Europeo de Desarrollo Regional (FEDER), the Spanish Ministerio de Ciencia e Innovación, under Grant No. TEC2008-06787.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Angarita, F., Sansaloni, T., Perez-Pascual, A. et al. Modified Shuffled Based Architecture for High-Throughput Decoding of LDPC Codes. J Sign Process Syst 68, 139–149 (2012). https://doi.org/10.1007/s11265-011-0592-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-011-0592-z