Abstract

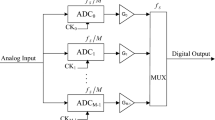

A scaling-friendly approach for the low-power calibration of oversampled analog-to-digital (A/D) systems is presented. A 22-dB amplifier relaxes the design constraints of the analog front-end (AFE). The integrator non-idealities in the AFE of the sigma-delta (ΣΔ) ADC are calibrated using a multi-rate polyphase least-mean squares (LMS) algorithm. The proposed half- (f s/2) and quarter-rate (f s/4) LMS calibration schemes reduce computational complexity and achieve more than 2.5× savings in digital power consumption for low-OSR (over-sampling ratio) ΔΣ ADCs, which require higher adaptive filter orders and sampling frequencies. The proposed scheme can have further applications in serial-link I/O and sub-band echo cancellation architectures.

Similar content being viewed by others

References

Peach, C. T., Moon, U.-K., & Allstot, D. J. (2010). An 11.1 mW 42 MS/s 10b ADC with two-step settling in 0.18 μm CMOS. IEEE Journal of Solid-State Circuits, 45, 391–400.

Rutten, R., Breems, L. J., & Wetzker, G. (2006). Digital calibration of a continuous-time cascaded ΣΔ modulator based on variance derivative estimation. IEEE Processing European Solid-State Circuits Conference, pp. 199–202.

Shu, Y.-S., Kamiishi, J., Tomioka, K., Hamashita, K., & Song, B.-S. (2010). LMS-Based noise leakage calibration of cascaded continuous-time modulators. IEEE Journal of Solid-State Circuits, 45, 368–379.

Bosi, A., Panigada, A., Cesura, G., & Castello, R. (2005). An 80 MHz 4X oversampled cascaded ΣΔ-pipeline ADC with 75 dB DR and 87 dB SFDR. IEEE International Solid- State Circuits Conference, pp. 174–175.

Murmann, B. (2006). Digitally assisted analog circuits. IEEE Micro, 26, 38–47.

Cauwenberghs, G., & Temes, G. C. (2000). Adaptive digital correction of analog errors in MASH ADCs-I. Off-line and blind on-line calibration. IEEE Transactions Circuits and Systems-II: Analog and Digital Signal Processing, 47, 621–628.

Kiss, P., Silva, J., Wiesbauer, A., Sun, T., Moon, U.-K., Stonick, J. T., et al. (2000). Adaptive digital correction of analog errors in MASH ADCs. II. Correction using test-signal injection. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 47, 629–638.

Gupta, S., Tang, Y., Cheng, K.-W., Paramesh, J., & Allstot, D. J. (2011). Multi-rate polyphase DSP and LMS calibration schemes for oversampled data conversion systems. IEEE Acoustics, Speech and Signal Processing Conference, pp.1585–1588.

Schreier, R., & Temes, G. C. (2004). Understanding delta sigma data converters. IEEE Wiley Press.

Tang, Y., Gupta, S., Paramesh, J., & Allstot, D. (2007). A digital-summing feedforward ΣΔ modulator and its application to a cascade ADC. IEEE International Symposium on Circuits and Systems, May pp. 485–488.

Diniz, P. R. (2002). Adaptive filtering: Algorithms and practical implementation (2nd ed.). Boston, MA: Kluwer Academic. Ch. 3.

Staszewski, R. B. (2000). A 550-MSample/s 8-Tap FIR digital filter for magnetic recording read channels. IEEE Journal of Solid-State Circuits, 35, 1205–1210.

Ahmed, N. Y., Ashour, M. A., & Nassar, A. M. (2009). Power efficient polyphase comb decimation filters for ΣΔ modulators in multi-rate digital receivers. European Conference on Circuit Theory and Design, pp. 719–722.

Oppenheim, A. V., & Schafer, R. W. (1989). Discrete-time signal processing. Englewood Cliffs, N.J.: Prentice Hall.

Mathe, L. K.-A. (2001). Noise cancellation circuit in a quadrature downconverter. U.S. Patent #6243430, June 5, 2001.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gupta, S., Tang, Y., Paramesh, J. et al. Multi-rate Polyphase DSP and LMS Calibration Schemes for Oversampled ADCs. J Sign Process Syst 69, 329–338 (2012). https://doi.org/10.1007/s11265-012-0677-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-012-0677-3