Abstract

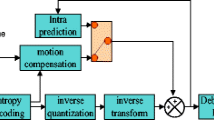

This paper presents a novel hardware architecture for the real-time high-throughput implementation of the adaptive deblocking filtering process specified by the H.264/AVC video coding standard. A parallel filtering order of six units is proposed according to the H.264/AVC standard. With a parallel filtering order (fully compliant with H.264/AVC) and a dedicated data arrangement in local memory banks, the proposed architecture can process filtering operations for one macroblock with less filtering cycles than previously proposed approaches. Whereas, filtering efficiency is improved due to a novel computation scheduling and a dedicated architecture composed of six filtering cores. It can be used either into the decoder or the encoder as a hardware accelerator for the processor or can be embedded into a full-hardware codec. This developed Intellectual Property block-based on the proposed architecture supports multiple and high definition processing flows in real time. While working at clock frequency of 150 MHz, synthesized under 65 nm low power and low voltage CMOS standard cell technology, it easily meets the throughput requirements for 4 k video at 30 fps of all the levels in H.264/AVC video coding standard and consumes 25.08 Kgates.

Access this article

We’re sorry, something doesn't seem to be working properly.

Please try refreshing the page. If that doesn't work, please contact support so we can address the problem.

Similar content being viewed by others

References

ISO/IEC 14 496 ISO/IEC MPEG and ITU-T (2003). AVC Draft ITU-T “ISO/IEC 14 496–10 Recommendation and final draft international standard of joint video specification”. ISO/IEC and ITU-T.

Richardson, I.E. (August 2003). H.264 and MPEG-4 video compression (320 pages). England edition. Wiley & Sons.

Wiegand, T., Sullivan, G. J., Bjontegaard, G., & Luthra, A. (2003). Overview of the H.264/AVC video coding standard. IEEE Transactions on Circuits and Systems for Video Technology, 13(7), 560–576.

Horowitz, M., Joch, A., Kossentini, F., Hallapuro, A. (July 2003). H.264/AVC baseline profile decoder complexity analysis. IEEE Transactions on Circuits and Systems for Video Technology, 13(7).

Khurana, G., Kassim, T., Chua, T., & Mi, M. (2006). A pipelined hardware implementation of in-loop deblocking filter in H.264/AVC. IEEE Transactions on Consumer Electronics, 52(2), 536–540.

Jing, H., Yan, H., Xinyu, X. (September 2009). An efficient architecture for deblocking filter in H.264/AVC. In the Proceedings of the Fifth International Conference on Intelligent Information Hiding and Multimedia Signal Processing (IIH-MSP’09) (pp. 848–851).

Chien, C.A., Chang, H.C., Gue, J.I. (November 30 - December 3 2008). A high throughput in-loop de-blocking filter supporting H.264/AVC BP/MP/HP video coding. In Proceedings of the IEEE Asia Pasific Conference on Circuits and Systems (APCCAS’08) (pp. 312–315).

Chen, K. H. (2010). 48 cycles-per-macro block deblocking filter accelerator for high-resolution H.264/AVC decoding. IET Circuits, Devices & Systems, 4(3), 196–206.

ITU (2008). H.264/AVC reference software decoder (v10.2). http://iphome.hhi.de/suehring/tml/doc/ldec/html.

Chen, C. M., & Chen, C. H. (2008). Configurable VLSI architecture for deblocking filter in H.264/AVC. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 16(8), 1072–1082.

Wei, H., Tao, L. I. N., & Zheng-hui, L. I. N. (2009). Parallel processing architecture of H.264 adaptive deblocking filters. Journal of Zhejiang University, 10(8), 1160–1168.

Tobajas, F., CalIicό, G. M., Perez, P. A., de Armas, V., & Sarmiento, R. (2008). An efficient double-filter hardware architecture for H.264/AVC deblocking filtering. IEEE Transactions on Consumer Electronics, 54(1), 131–139.

Xu, K., & Choy, C. S. (2008). Five-stage pipeline, 204 cycles/MB, single-port SRAM-based deblocking filter for H.264/AVC. IEEE Transactions on Circuits and Systems for Video Technology, 18(3), 363–374.

Lin, Y. C., & Lin, Y. L. (2009). A two-result-per-cycle deblocking filter architecture for QFHD H.264/AVC decoder. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 17(6), 838–843.

SYSTEM@TIC ICT cluster. http://www.systematic-paris-region.org/.

Acknowledgments

This present study was carried out for the RTEL4I project and funded by the French SYSTEM@TIC ICT cluster [15].

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kthiri, M., Le Gal, B., Kadionik, P. et al. A Very High Throughput Deblocking Filter for H.264/AVC. J Sign Process Syst 73, 189–199 (2013). https://doi.org/10.1007/s11265-013-0744-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-013-0744-4