Abstract

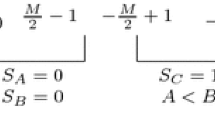

The three-moduli set {2n,2n − 1,2n+ 1 − 1} started to receive more attention lately. This moduli set is considered an arithmetic-friendly set because it avoids the demanding channel (2n + 1) of the traditional 3-moduli set {2n,2n − 1,2n + 1}. This work considers an enhanced form of the above moduli set, {2n + k,2n − 1,2n+ 1 − 1}, and proposes a sign identifier for numbers within the dynamic range of the set. While the published sign identifiers have dealt with the unextended form {2n,2n − 1,2n+ 1 − 1}, this is the first sign identifier that deals with the extended form. Based on VLSI layout synthesis for the case (k = 0), the proposed structure has less or similar area and power requirements, nevertheless, it achieves an improved time performance in the range of (13.0–29.6)% compared with the most recent sign identifiers. When compared with a recently published residue-to-binary converter for the moduli set {2n + k,2n − 1,2n− 1 − 1}, which can function as a converter-based sign identifier, the proposed detector has on average reduced area, time, and power by 175%, 106%, and 60%, respectively.

Similar content being viewed by others

References

Soderstrand, M.A., Jenkins, W.K., Jullien, G., Taylor, F. (Eds.) (1986). Residue number system arithmetic: modern applications in digital signal processing. New York: IEEE Press.

Mohan, P.V. (2016). Residue number systems: theory and applications. Birkhauser: Switzerland.

Hiasat, A. (2004). A suggestion for a fast residue multiplier for a family of moduli of the form (2n − (2p ± 1)). Computer Journal, 47(1), 93–102.

Sousa, L., Antao, A., Martins, P. (2016). Combining residue arithmetic to design efficient cryptographic circuits and systems. IEEE Circuits and Systems Magazine, 16(4), 6–32.

Hiasat, A., & Al-Khateeb, A. (1998). Efficient digital sweep oscillator with extremely low sweep rates. IEE CD&S, 145(6), 409–414.

Dutta, C.B., Garai, P., Sinha, A. (2012). Design of a reconfigurable DSP processor with bit efficient residue number system. International Journal of VLSI Design & Commmunication System (VLSICS), 3(5), 175–189.

Wei, J., Guo, W., Liu, H., Tan, Y. (2013). A unified cryptographic processor for RSA and ECC in RNS. In Communications in computer and information science (pp. 19–32). Berlin: Springer.

Hiasat, A., & Zohdy, H. (1997). Design and implementation of an RNS division algorithm. In IEEE symposium on computer arithmetic (pp. 240–249).

Hiasat, A. (1993). New designs for a sign detector and a residue to binary converter. IET Proceedings - Circuits, Devices and Systems, 140(4), 247–252.

Bi, S., & Gross, W. (2008). The mixed-radix Chinese remainder theorem and its applications to residue comparison. IEEE Transactions on Computers, 57(12), 1624–1632.

Tomczak, T. (2008). Fast sign detection for RNS (2n − 1, 2n, 2n + 1). IEEE Transactions on Circuits and Systems I, 55(6), 1502–1511.

Pettenghi, H., Chaves, R., Sousa, L. (2004). (2n + 1, 2n + k, 2n − 1): a new RNS moduli set extension. In Proceedings of the EUROMICRO systems on digital system design (DSD’04) (pp. 210–217).

Xu, M., Yao, R., Luo, F. (2012). Low-complexity sign detection algorithm for RNS {2n − 1, 2n, 2n + 1}. IEICE Transactions on Electronics, 95(9), 1552–1556.

Kumar, S., & Chang, C.-H. (2016). New fast and area-efficient adder-based sign detector for RNS 2n − 1, 2n, 2n + 1. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(7), 2608–2612.

Sousa, L., & Martins, P. (2016). Sign detection and number comparison on RNS 3-moduli sets {2n − 1, 2n + x, 2n + 1}. Circuits, Systems, and Signal Processing, 36(3), 1224–1246.

Hiasat, A. (2016). A sign detector for a group of three-moduli sets. IEEE Transactions on Computers, 65(12), 3580–3590.

Xu, M., Bian, Z., Yao, R. (2015). Fast sign detection algorithm for the RNS moduli set {2n+ 1 − 1, 2n − 1, 2n}. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23(2), 379– 383.

Niras, C.V., & Kong, Y. (2016). Fast sign-detection algorithm for residue number system moduli set {2n − 1, 2n, 2n+ 1 − 1}. IET Computers and Digital Techniques, 10(2), 54–58.

Chang, C.-H., & Kumar, S. (2017). Area-efficient and fast sign detection for four-moduli set RNS (2n − 1, 2n, 2n + 1, 22n + 1). IEEE International Symposium on Circuits and Systems (ISCAS), 1540–1543.

Hiasat, A. (2017). A reverse converter and sign detectors for an extended RNS five moduli set. IEEE Transactions on Circuits and Systems TCAS-I, 64(1), 111–121.

Hiasat, A. (2018). A sign detector for the extended four moduli set {2n − 1, 2n, + 1, 22n + 1, 2n + k}. IET Proceedings - Computers and Digital Techniques, 12(2), 39–44.

Kumar, S., Chang, C.-H., Tay, T.F. (2017). New algorithm for signed integer comparison in {2n + k, 2n − 1, 2n + 1, 2n± 1 − 1} and its efficient hardware implementation. IEEE Transactions on Circuits and Systems TCAS-I, 64(6), 1481–1493.

Zimmerman, R. (1999). Efficient VLSI implementation of modulo (2n1) addition and multiplication. In Proceedings of the 14th IEEE symposium on computer arithmetic (pp. 158–167).

Piestrak, S., & Berezowski, K. (2008). Design of residue multipliers-accumulators using periodicity. In Proceedings of the IET Irish signals and systems conference (ISSC) (pp. 380–385).

Sheu, M.-H., Siao, S.-M., Hwang, Y.-T., Sun, C.-C., Lin, Y.-P. (2016). New adaptable three-moduli {2n + k, 2n,− 1, 2n− 1 − 1} residue number system-based finite impulse response implementation. IEICE Electronics Express, 13, 1–9.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Hiasat, A., Sousa, L. Sign Identifier for the Enhanced Three Moduli Set {2n + k, 2n − 1, 2n+ 1 − 1}. J Sign Process Syst 91, 953–961 (2019). https://doi.org/10.1007/s11265-018-1434-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-018-1434-z