Abstract

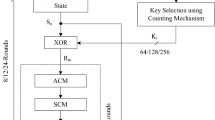

This paper proposes a low-power advanced encryption standard (AES) that can be utilized in smaller applications such as small-scale internet- of-things (IoT) devices. The proposed AES uses 8-bit and 32-bit datapaths to satisfy low power consumption and small area requirements. We use the 32-bit datapath in MixColumns only; the 8-bit datapath was used in other blocks such as SubBytes, Byte Permutation, AddRoundKey, and KeyExpansion. In addition, we propose optimized SubBytes and MixColumns to achieve low power consumption within a small area. To optimize SubBytes, we simplify the algorithm block-by-block to decrease the area. For the MixColumns, we present a 32-bit datapath that uses the proposed 0 × 02 and 0 × 03 multiplier. The AES that we have presented in this study, is implemented through Verilog-HDL and synthesized using the Samsung 65 nm standard cell library. The proposed AES shows 5400 2-input NAND gate equivalences and a power consumption of 10.01 μW (@ 0.9 V) at 10 MHz.

Similar content being viewed by others

References

Roman, R., Najera, P., & Lopez, J. (2011). Securing the internet of things. Computer, 44(9), 51–58.

Barki, A., Bouabdallah, A., Gharout, S., & Traore, J. (2016). M2M security: Challenges and solutions. IEEE Commun. Surveys Tuts., 18(2), 1241–1254.

Keoh, S. L., Kumar, S., & Tschofenig, H. (2014). Securing the internet of things: A standardization perspective. IEEE Internet Things, 1(3), 265–275.

Yu, W., & Kose, S. (2017). A lightweight masked AES implementation for securing IoT against CPA attacks. IEEE Transactions on Circuits and Systems I: Regular Papers, 64(11), 2934–2944.

Tsai, K., Huang, Y., Leu, F., You, I., Huang, Y., & Tsai, C. (2018). AES-128 based secure low power communication for LoRaWAN IoT environments. IEEE Access, 6, 45325–45334.

Niu, Y., Zhang, J., Wang, A., & Chen, C. (2019). An efficient collision power attack on AES encryption in edge computing. IEEE Access, 7, 18734–18748.

Bui, D., Puschini, D., Bacles-Min, S., Beigne, E., & Tran, X. (2017). AES Datapath optimization strategies for low-power low-energy multisecurity-level internet-of-things applications. IEEE VLSI Syst., 25(12), 3281–3290.

Agwa, S., Yahya, E., & Ismail, Y. (2017). Power efficient AES core for IoT constrained devices implemented in 130nm CMOS. In Proc. 2017 IEEE ISCAS, Baltimore, pp. 1–4.

National Institute of Standard Technology (NIST) (2001). Federal Information Processing Standards (FIPS) publication 197. Advanced Encryption Standard.

Wang, Y., & Ha, Y. (2013). FPGA-based 40.9-Gbits/s masked AES with area optimization for storage area network. IEEE Transactions on Circuits and Systems II: Express Briefs, 60(1), 36–40.

Wong, M. M., Wong, M. L. D., Nandi, A. K., & Hijazin, I. (2012). Construction of optimum composite Fied architecture for compact high-throughput AES S-boxes. IEEE VLSI Syst., 20(6), 1151–1155.

El-meligy, N., Anin, M., Yahya, E., & Ismail, Y. (2017). 130nm low power asynchronous AES Core. In Proc. 2017 IEEE ISCAS, Baltimore, pp. 1–4.

Good, T., & Benaissa, M. (2010). 692-nW advanced encryption standard (AES) on a 0.13-μm CMOS. IEEE VLSI Syst., 18(12), 1753–1757.

Hocquet, C., Kamel, D., Regazzoi, F., Legat, J., Flandre, D., Bol, D., & Standaert, F. (2011). Harvesting the potential of nano-CMOS for lightweight cryptography an ultra-low-voltage 65 nm AES coprocessor for passive RFID tags. JCEN, 1(1), 79–86.

Shastry, P., Agnihotri, A., Kachhwaha, D., Singh, J., & Sutaone, M. (2011). A combinational logic implementation of S-box of AES. In Proc. 2011 IEEE 54th International MWSCAS, Seoul, pp. 1–4.

Zhao, W., Ha, Y., & Alioto, M. (2015). AES architectures for minimum-energy operation and silicon demonstration in 65nm with lowest energy per encryption. In Proc. 2015 IEEE ISCAS, Lisbon, pp. 2349–2352.

Mathew, S., Satpathy, S., Suresh, V., Anders, M., Kaul, H., Agarwal, A., Hsu, S., Chen, G., & Krishnamurthy, R. (2015). 340 mV-1.1 V, 289 Gbps/W, 2090-gate NanoAES hardware accelerator with area-optimized encrypt/decrypt GF(24)2 polynomials in 22 nm tri-gate CMOS. IEEE Journal of Solid-State Circuits, 50(4), 1048–1058.

Acknowledgments

This research was supported by the Ministry of Science and ICT (MSIT), Korea, under the Information Technology Research Center (ITRC) support program (IITP-2019-2016-0-00309) supervised by the Institute for Information & communications Technology Planning & Evaluation (IITP) and the National Research Foundation of Korea by the Korea government (NRF-2017R1A2A2A05001046).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kim, H.K., Sunwoo, M.H. Low Power AES Using 8-Bit and 32-Bit Datapath Optimization for Small Internet-of-Things (IoT). J Sign Process Syst 91, 1283–1289 (2019). https://doi.org/10.1007/s11265-019-01471-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-019-01471-8