Abstract

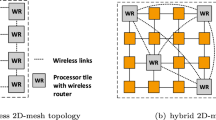

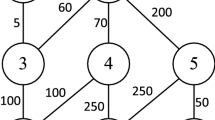

The increased latency and power consumption are the major challenges of traditional wired Network-on-Chip (NoC). The Wireless NoC (WNoC) architecture is regarded as a novel approach to solve NoC problems. In this paper, hybrid hierarchical structures are studied. The considered topologies for the first level of the hierarchy include: Chordal Ring of degree 3 (CR) and Ring-Connected Cycles (RCC). On the second level of the hierarchy, inspired by the Traveling Salesman Problem (TSP), a new method is proposed to form the topology. Considering the NP-Hard nature of the problem, the hybrid PS-ACO algorithm is used to obtain the desired tour. In this paper, the uniform random traffic is used as the synthetic traffic pattern and the 3-tuple traffic is used as a real application traffic pattern. The simulation results show that the proposed structure has fewer wired links and considerably increased efficiency compared with a wired mesh topology in NoC.

Similar content being viewed by others

References

ITRS. (2011). Edition—system drivers (2011).

Benini, L., & De Micheli, G. (2002). Network on chip: A new paradigm for systems on chip design. In Proceedings of design, automation and test in Europe conference and exhibition (pp. 418–419).

Semiconductor Industry Association. (2009). ITRS: International technology roadmap for semiconductors. [Online]. Available: http://www.itrs.net/reports.html.

Semiconductor Industry Association. (2012). ITRS: International technology roadmap for semiconductors. [Online]. Available: http://www.itrs.net/reports.html.

Karkar, A., Mak, T., Tong, K.-F., & Yakovlev, A. (2016). A survey of emerging interconnects for on-chip efficient multicast and broadcast in many-cores. IEEE Circuits and Systems Magazine, 16(1), 58–72.

Pavlidis, V., & Friedman, E. (2006). 3-D Topologies for networks-on-chip. In IEEE international SOC conference (pp. 285–288).

Shacham, A., Bergman, K., & Carloni, L. (2008). Photonic networks-on-chip for future generations of chip multiprocessors. IEEE Transactions on Computers, 57(9), 1246–1260.

Chang, M., Cong, J., Kaplan, A., Naik, M., Reinman, G., Socher, E., & Tam, S.-W. (2008). CMP network-on-chip overlaid with multi-band RF-interconnect. In Proceedings of IEEE international symposium high-performance computer architecture (HPCA) (pp. 191–202).

Carloni, L., Pande, P., & Xie, Y. (2009). Network-on-chip in emerging interconnect paradigms: Advantages and challenges. In Proceedings of 3rd ACM/IEEE international symposium network-on-chip (pp. 93–102).

Wang, S., & Jin, T. (2014). Wireless network-on-chip: A survey. The Journal of Engineering, 1(1), 1–7. https://doi.org/10.1049/joe.2013.0209.

Ganguly, A., Chang, K., Deb, S., Pande, P. P., Belzer, B., & Teuscher, C. (2011). Scalable hybrid wireless network-on-chip architectures for multicore systems. IEEE Transactions on Computers, 60(10), 1485–1502.

Burke, P. J., Li, S., & Yu, Z. (2006). Quantitative theory of nanowire and nanotube antenna performance. IEEE Transactions on Nanotechnology, 5(4), 314–334.

Kempa, K., et al. (2007). Carbon nanotubes as optical antennae. Advanced Materials, 19, 421–426.

Deb, S., Chang, K., Yu, X., Sah, S. P., Cosic, M., Ganguly, A., et al. (2013). Design of an energy-efficient CMOS-compatible NoC architecture with millimeter-wave wireless interconnects. IEEE Transactions on Computers, 62(12), 2382–2396.

Tomassini, M., Giacobini, M., & Darabos, C. (2005). Evolution and dynamics of small-world cellular automata. Complex Systems, 15(4), 261–284.

Murray, J., Wettin, P., Pande, P., & Shirazi, B. (2016). Sustainable wireless network-on-chip architectures. San Francisco, CA: Morgan Kaufmann.

Chien, A. (1998). A cost and speed model for k-ary n-cube wormhole routers. IEEE Transactions on Parallel and Distributed Systems, 9(2), 150–162.

Duato, J., Yalamanchili, S., & Ni, L. (2003). Interconnection networks an engineering approach. San Francisco, CA: Morgan Kaufmann.

Mineo, A., Palesi, M., Ascia, G., & Catania, V. (2016). Exploiting antenna directivity in wireless NoC architectures. Microprocessors and Microsystems, 43, 59–66.

Schrijver, A. (2005). On the history of combinatorial optimization. Amsterdam: Elsevier.

Aarts, E. H. L., de Bont, F. M. J., Habers, E. H. A., & van Laarhoven, P. J. M. (1986). Parallel implementations of the statistical cooling algorithm. Integration, the VLSI Journal, 4(3), 209–238.

Catthoor, F., & de Man, H. (1988). SAMURAI: A general and efficient simulated-annealing schedule with fully adaptive annealing parameters. Integration, the VLSI Journal, 6(2), 147–178.

Shuang, B., Chen, J., & Li, Z. (2011). Study on hybrid PS-ACO algorithm. Applied Intelligence, 34, 64–73.

El-Rewini, H., & Abd-El-Barr, M. (2005). Advanced computer architecture and parallel processing. Hoboken, NJ: Wiley.

Arden, B. W., & Lee, H. (1981). Analysis of chordal ring network. IEEE Transactions on Computers, 30(4), 291–295.

Parhami, B. (2002). Introduction to parallel processing algorithms and architectures. New York, NY: Kluwer Academic Publishers.

Kim, K., Yoon, H., & Kenneth, K. O. (2000). On-chip wireless interconnection with integrated antennas. In Electron devices meeting (pp. 485–488).

Floyd, B., Hung, C.-M., & Kenneth, K. O. (2002). Intra-chip wireless interconnect for clock distribution implemented with integrated antennas, receivers, and transmitters. IEEE Journal of Solid-State Circuits, 37(5), 543–552.

Zhao, D., & Wang, Y. (2008). SD-MAC: Design and synthesis of a hardware-efficient collision-free QoS-aware MAC protocol for wireless network-on-chip. IEEE Transactions on Computers, 57(9), 1230–1245.

Zhao, D., Wang, Y., Li, J., & Kikkawa, T. (2011). Design of multi-channel wireless noc to improve on-chip communication capacity. In Fifth ACM/IEEE international symposium on network-on-chip (pp. 177–184).

Pande, P. P., Ganguly, A., Chang, K., & Teuscher, C. (2009). Hybrid wireless network on chip: A new paradigm in multi-core design. In 2nd International workshop on network on chip architectures (pp. 71–76).

Kirkpatrick, S., Gelatt, C., Jr., Vecchi, M., & McCoy, A. (1983). Optimization by simulated annealing. Science, 220(4598), 671–679.

Jamali, M. A. J., & Khademzadeh, A. (2009). MinRoot and CMesh: Interconnection architectures for network-on-chip systems. International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering, 3(6), 1303–1308.

Chariete, A., Bakhouya, M., Gaber, J., & Wack, M. (2015). A design space exploration methodology for customizing on-chip communication architectures: Towards fractal NoCs. Integration, the VLSI Journal, 50, 158–172.

Deb, S., Ganguly, A., Chang, K., Pande, P., Belzer, B., & Heo, D. (2010). Enhancing performance of network-on-chip architectures with millimeter-wave wireless interconnects. In The 21st IEEE international conference on application-specific systems architectures and processors.

Wang, C., Hu, W.-H., & Bagherzadeh, N. (2011). A wireless network-on-chip design for multicore platforms. In Proceedings of 19th euromicro international parallel, distributed and network-based processing (PDP) conference (pp. 409–416).

Wang, C., Hu, W.-H., & Bagherzadeh, N. (2012). A load-balanced congestion-aware wireless network-on-chip design for multicore platforms. Microprocessor and Microsystems, 36(7), 555–570.

Hu, W.-H., Wang, C., & Bagherzadeh, N. (2015). Design and analysis of a mesh-based wireless network-on-chip. Journal of Supercomputing, 71(8), 2830–2846.

Rezaei, A., Daneshtalab, M., Safaei, F., & Zhao, D. (2016). Hierarchical approach for hybrid wireless network-on-chip in many-core era. Computers & Electrical Engineering, 51, 225–234.

Bahrami, B., Jamali, M. A. J., & Saeidi, S. (2016). Proposing an optimal structure for the architecture of wireless networks on chip. Telecommunication Systems, 62, 199–214.

Dai, P., Chen, J., Zhao, Y., & Lai, Y.-H. (2015). A study of a wire–wireless hybrid NoC architecture with an energy-proportional multicast scheme for energy efficiency. Computers & Electrical Engineering, 45, 402–416.

Abadal, S., Nemirovsky, M., Alarcón, E., & Cabellos-Aparicio, A. (2015). Networking challenges and prospective impact of broadcast-oriented wireless networks-on-chip. In Proceedings of the ACM/IEEE NoCS.

Abadal, S., Mestres, A., Nemirovsky, M., Lee, H., González, A., Alarcón, E., et al. (2016). Scalability of broadcast performance in wireless network-on-chip. IEEE Transactions on Parallel and Distributed Systems, 27(12), 3631–3645.

Kennedy, J., & Eberhart, R. (1995). A new optimizer using particle swarm theory. In Proceedings of the sixth international symposium on micromachine and human science.

Dorigo, M., & Stutzle, T. (2004). Ant colony optimization. Cambridge, MA: MIT Press.

Shamim, M.-S., Mansoor, N., Narde, R.-S., Kothandapani, V., Ganguly, A., & Venkataraman, J. (2017). A wireless interconnection framework for seamless inter and intra-chip communication in multichip systems. IEEE Transactions on Computers, 66, 389–402.

Ben-Itzhak, Y., Zahavi, E., Cidon, I., & Kolodny, A. (2012). HNOCS: Modular open-source simulator for Heterogeneous NoCs. In SAMOS conference (pp. 51–57).

Soteriou, V., Eisley, N., Wang, H., Li, B., & Peh, L.-S. (2006). Polaris: A system-level roadmap for on-chip interconnection networks. In International conference on computer design (pp. 134–141).

Pande, P. P., Grecu, C., Jones, M., Ivanov, A., & Saleh R. (2005). Effect of traffic localization on energy dissipation in NoC-based interconnect. In IEEE international symposium on circuits and systems (pp. 1774–1777).

Dally, W., & Towles, B. (2003). Principles and practices of interconnection networks. San Francisco, CA: Morgan Kaufmann.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bahrami, B., Jabraeil Jamali, M.A. & Saeidi, S. A hierarchical architecture based on traveling salesman problem for hybrid wireless network-on-chip. Wireless Netw 25, 2187–2200 (2019). https://doi.org/10.1007/s11276-017-1641-8

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11276-017-1641-8