Abstract

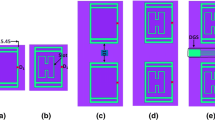

The proposed work presents a co-design approach for a new asymmetric rectangular cross shaped slotted patch antenna with low noise amplifier that occupies 17.2–25.8 GHz wide-band for SDR applications. This co-design approach minimizes the chip area and noise and also improves integration system over the bandwidth of 8.6 GHz. Three different architectures have been designed in this work. Firstly, a two stage CMOS CG–CS LNA is designed using a technique of series–parallel resonant network as an input matching network and as inter-stage matching network between CG and CS LNA. In second architecture stage, a rectangular shaped microstrip antenna is designed and a slot of asymmetric cross shape is cut on the patch antenna. In third architecture the slotted antenna is integrated with low noise amplifier in order to form a co-design approach in which series–parallel resonant network is used as a band pass filter between slotted patch antenna and LNA. A two-stage CMOS LNA design is simulated and layout is made using foundry design kit for the TSMC 65 nm CMOS process in ADS.v.12. A simulation result of LNA achieves S11 of −21.4 dB with gain ranging from 7.4 to 21.3 dB over the wide-band of 19.1–28.8 GHz. The slotted antenna achieves S11 of −19 dB at 26 GHz and covers frequency range of 20.1–27.8 GHz with good radiation and receiving patterns. This co-design approach is analysed considering the 50 Ω impedance matching throughout the design and simulated on the platform of ADS.v.12. The best achievement of proposed co-design approach is reduced noise figure which is most suitable for SDR applications.

Similar content being viewed by others

References

Brandolini, M., Rossi, P., Manstretta, D., & Svelto, F. (2005). Towards multistandard mobile terminals—Fully integrated receiver requirements and architectures. IEEE Transactions on Microwave Theory and Techniques, 53(3), 1026–1038.

Abidi, A. A. (2007). The path to the software-defined radio receiver. IEEE Journal of Solid-State Circuits, 42(5), 954–967.

Mitola, J. (1995). The software radio architecture. IEEE Communications Magazine, 33(5), 26–38.

Osmany, S. A., Herzel F., & Scheytt, J. C. (2009). An integrated 0.6–4.6 GHz, 5–7 GHz, 10–14 GHz, and 20–28 GHz frequency synthesizer for software-defined radio applications. In Proceedings of the IEEE bipolar/BiCMOS circuits and technology meeting (BCTM 2009), Capri, Italy (pp. 39–42).

Zolfaghari, A., & Razavi, B. (2003). A low-power 2.4-GHz transmitter/receiver CMOS IC. IEEE Journal of Solid-State Circuits, 38, 177–181.

Pandey, G. P., Kanauajia, B. K., Guatam, A. K., & Gupta, S. K. (2013). Ultra wideband L-strip proximity coupled slot loaded circular microstrip antenna for modern communication systems. Wireless Personal communication, 70, 139–151.

Kumar, S., Kanaujia, B. K., Dwari, S., Pandey, G. P., & Singh, D. K. (2015). A miniurazation approach towards 40 GHz single chip receiver system for MMW Communication networks. Wireless Personal Communication. doi:10.1007/s11277-015-2688-4.

Bevilacqua, A., & Niknejad, A. M. (2004). An ultrawideband CMOS low noise amplifier for 3.1–10.6-GHz wireless receivers. IEEE Journal of Solid-State Circuits, 39(12), 2259–2268.

Lin, Y. J., Hsu, S. S. H., Jin, J. D., & Chan, C. Y. (2007). A 3.1–10.6 GHz ultrawideband CMOS low noise amplifier with current-reused technique. IEEE Microwave Wireless Compon. Lett., 17(3), 232–234.

Vecchi, F. (2010). A wideband mm-wave CMOS receiver for Gb/s communications employing interstage coupled resonator. In Proceedings of the IEEE international solid-state conference (pp. 220–221).

El-Nozahi, M., Sanchez-Sinencio, E., & Entesari, K. (2010). A millimeterwave (23–32 GHz) wideband BiCMOS low-noise amplifier. IEEE Journal of Solid-State Circuits, 45(2), 289–299.

Lo, Y. T., & Kiang, J. F. (2011). Design of wideband LNAs using parallel to series resonant matching network between commom-Gate and common-source stage. IEEE Transactions on Microwave Theory and Techniques, 59(9), 2285–2293.

Bories, S., Pelissier, M., Delaveaud, C., & Bourtoutian, R. (2007). Performances Analysis of LNA-antenna co-design for UWB system. Antennas and Propagation EuCAP, 34, 1–5.

Shaeffer, D. K., & Lee, T. H. (1997). A 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE Journal of Solid-State Circuits, 32, 745–759.

Allstot, D. J., Li X., & Shekhar, S. (2004). Design considerations for CMOS low-noise ampliifers. In Proceedings of the IEEE radio frequency integrated circuits (RFIC) symposium (pp. 97–100).

Wang, Hongrui, Zhang, Lei, Zhang, Li, Wang, Yan, & Zhiping, Yu. (2011). Design of 24-GHz high-gain receiver front-end utilizing ESD-split input matching network. IEEE Transactions on Circuits and Systems, 58(8), 482–486.

Liu, L. C., Liu, C. S., Kessler, J. R., Kuo Wang, S., & Chang, C. D. (1986). A 30-GHz monolithic receiver. IEEE Transactions on Microwave Theory and Techniques, 33(12), 2079–2083.

Queudet, F., Pele, I., Froppier, B., Mahe, Y., & Toutain, S. (2002).Integration of pass-band filters in patch antennas. 32nd European microwave conference, Milan, vol.35, pp. 685–688.

Chen, K. H., Lu, J. H., Chen, B. J., & Liu, S. I. (2007). An ultra-wideband 0.4–10 GHz LNA in 0.18 µm CMOS. IEEE Transactions on Circuits and Systems II: Express Briefs, 54, 217–221.

Lin, Y. S., Chen, C. Z., Yang, H. Y., Chen, C. C., Lee, J. H., Huang, G. W., et al. (2010). Analysis and design of a CMOS UWB LNA with dual—RLC-branch wideband input matching network. IEEE Transactions on Microwave Theory and Techniques, 58(2), 287–296.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kumar, S., Kanaujia, B.K., Dwari, S. et al. Co-design Approach for Wide-Band Asymmetric Cross Shaped Slotted Patch Antenna with LNA. Wireless Pers Commun 85, 863–877 (2015). https://doi.org/10.1007/s11277-015-2814-3

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-015-2814-3