Abstract

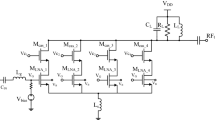

In this work, variation in threshold voltage is optimized for tunable body biasing CMOS power amplifier (PA). A two stage tunable biasing circuit is designed and integrated with class AB PA which improves variability in threshold voltage. Three most popular materials gallium arsenide, silicon and gallium nitride with two predictive technology model of 65 and 45 nm are employed for the analysis of threshold voltage optimization. A conventional single stage of tunable body biasing class AB PA is compared with a proposed PA of two stages. This concept demonstrates that threshold voltage variation can be lowered further if body biasing circuit is employed on the subsequent higher stages. The adaptive two stage body biasing design with class AB PA is analyzed with derived analytical equations. The calculated results shows gallium arsenide offers minimum variability in threshold voltage as compared to silicon and gallium nitride. Additionally, this class AB PA topology is simulated and fabricated for silicon material using 45 nm CMOS technology. The simulation results improve the robustness of the circuit in terms of performance parameters. S-parameter analysis is done that gives good agreement between simulated and measured results.

Similar content being viewed by others

References

Kumar, S. V., Kim, C. H., & Sapatnekar, S. S. (2006). Impact of NBTI on SRAM read stability and design for reliability. In Proceedings of the 7th International symposium on quality electronic design (pp. 210–218).

Turner, T. E. (2006). Design for reliability. In Proceedings of international physics failure analysis (pp. 257–264).

Cheng, B., Roy, S., & Asenov, A. (2007). CMOS 6-T SRAM cell design subject to atomistic fluctuations. Solid State Electronics, 51, 565–571.

Atkinson, A. J. (1985). Power devices in gallium arsenide. IEEE Solid State and Electron Devices Letters, 132, 264–271.

Baliga, B. J., Adler, M. S., & Oliver, D. W. (1982). Optimum semiconductor for power field effect transistors. IEEE Electron Devices Letters, 2, 162–164.

Yuan, J. S., & Tang, H. (2008). CMOS RF design for reliability using adaptive gate–source biasing. IEEE Transactions on Electron Devices, 55, 2348–2353.

Li, Y., Hwang, C.-H., & Li, T.-Y. (2009). Random-dopant-induced variability in nano-CMOS devices and digital circuits. IEEE Transactions on Electron Devices, 56, 1588–1597.

Ye, Y., Gummalla, S., Wang, C.-C., Chakrabarti, C., & Cao, Y. (2010). Random variability modeling and its impact on scaled CMOS circuits. Journal of Computational Electronics, 9, 108–113.

Kuhn, K., Kenon, C., Kornfeld, A., Liu, M., Maheshwari, A., Shih, W.-K., et al. (2008). Managing process variation in Intel’s 45 nm CMOS technology. Intel Technology Journal, 12, 93–109.

Bhushan, M., Gattiker, A., Ketchen, M. B., & Das, K. K. (2006). Ring oscillator for CMOS process tuning and variability control. IEEE Transactions on Semiconductor Manufacturing, 19, 10–18.

Lee, K.-F., Li, Y., Li, T.-Y., Su, Z.-C., & Hwang, C.-H. (2010). Device and circuit level suppression technique for random-dopant-induced static noise margin fluctuation in 16-nm-gate SRAM cell. Microelectronics Reliability, 50, 647–651.

Liu, Y., & Yuan, J.-S. (2011). CMOS RF low-noise amplifier design for variability and reliability. IEEE Transactions on Device and Materials Reliability, 11, 450–457.

Liu, Y., & Yuan, J.-S. (2011). CMOS RF power amplifier variability and reliability resilient biasing design and analysis. IEEE Transactions on Electron Devices, 58, 540–546.

Acknowledgments

The foundry design kit and chip Implementation is done by Film electronics Pvt ltd. We would like to thanks Mr. Kamal and Mr. Ankur kumar gupta for supporting our work during the fabrication process.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kumar, S., Handa, M., Bhasin, H. et al. Optimized Threshold Voltage Variation for Tunable Body Biasing CMOS Power Amplifier. Wireless Pers Commun 91, 439–452 (2016). https://doi.org/10.1007/s11277-016-3469-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-016-3469-4