Abstract

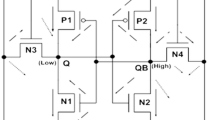

A dynamic threshold voltage control strategy is presented in this paper to minimize leakage power while enhancing the speed and stability. The threshold voltage of driver and access transistor are tuned dynamically through a novel body-bias controller circuit. The word line signal level controls the action of the proposed body-bias controller. In order to reduce subthreshold leakage current, the threshold voltage of NMOS access and driver transistors are adjusted to a high value by applying a reverse body-bias. On the other hand, forward body-bias lowers the threshold voltage of NMOS access transistor thereby enabling faster read and writes operation. Simulation results shows that the proposed design is much better than conventional and other SRAM cells such as, NC SRAM, PP SRAM, WRE8T. The amount of leakage power reduction is as high as 41.071 % over conventional 6T SRAM cell when tested on (8 × 16) SRAM array. Whereas, the improvement in read and write delay is 30 and 15.81 % respectively.

Similar content being viewed by others

References

Prince, B. (1991). Semiconductor memories. New York: Wiley.

International Technology Roadmap for Semiconductors. (2012). http://www.itrs.net/Links/2012ITRS/Home2012.htm.

Yamaoka, M., & Kawahara, T. (2007). Operating-margin-improved SRAM with column-at-a-time body-bias control technique. In Proceedings of the european solid-state circuits conference (ESSCIRC) (pp. 396–399).

Yang, Y., Park, J., Song, S. C., Wang, J., Yeap, G., & Jung, S. O. (2015). Single-ended 9T SRAM cell for near-threshold voltage operation with enhanced read performance in 22-nm FinFET technology. IEEE Transaction on Very Large Scale Integration, 23(11), 2748–2752.

Dreslinski, R. G., Wieckowski, M., Blaauw, D., Sylvester, D., & Mudge, T. (2010). Near-threshold computing: reclaiming Moore’s law through energy efficient integrated circuits. Proceedings IEEE, 98(2), 253–266.

Sinha, S., & Chaudhury, S. (2013). Impact of oxide thickness on gate capacitance—A comprehensive analysis on MOSFET, nanowire FET, and CNTFET devices. IEEE Transaction on Nanotechnology, 12(6), 958–965.

Seevinck, E., List, F. J., & Lohstroh, J. (1987). Static noise margin analysis of MOS SRAM cells. IEEE Journal of Solid State Circuits, 22(5), 748–754.

Takeda, K., Ikeda, H., Hagihara, Y., Nomura, M., & Kobatake, H. (2006). Redefinition of write margin for next-generation SRAM and write-margin monitoring circuit. In Proceedings international solid-state circuits conference (pp. 630–631).

Calhoun, B. H., & Chandrakasan, A. (2005). Analysing static noise margin for sub-threshold SRAM in 65 nm CMOS. In Proceedings ESSCIRC (pp. 363–366).

Chaudhury, S., Sistla, K. T., & Chattopadhyay, S. (2009). Genetic algorithm based FSM synthesis with area and power trade-offs. Proceedings Integration the VLSI Journal, Elsevier, 42(3), 376–384.

Yamaoka, M., Maeda, N., Shinozaki, Y., Shimazaki, Y., Nii, K., & Shimada, S., et al. (2005). Low-power embedded SRAM modules with expanded margins for writing. In Proceedings ISSCC (pp. 480–611).

Nho, H., Kolar, P., Hamzaoglu, F., Wang, Y., Karl, E., & Ng, Y. G., et al. (2010). A 32 nm high-k metal gate SRAM with adaptive dynamic stability enhancement for low-voltage operation. In Proceedings IEEE international solid-state circuits conference (ISSCC) (pp. 346–347).

Ananthan, H., Kim, C. H., & Roy, K. (2004). Larger than—Vdd forward body bias in sub-0.5v nanoscale CMOS. In Proceedings ISLPED (pp. 8–13).

Kao, J. T., & Chandrakasen, A. (2000). Dual-threshold voltage techniques for low-power digital circuits. IEEE Journal of Solid State Circuits, 7(35), 1009–1018.

Kao, J., Chandrakasan, A., & Antoniadis, D. (1997). Transistor sizing issues and tool for multi-threshold CMOS technology. In Proceedings of design automation conference (pp. 409–414).

Kang, S., & Leblebici, Y. (2003). CMOS digital integrated circuits. New York: Mc-Graw hill.

Elakkumanan, P., Thondapu, C., & Sridhar, R. (2004). A gate leakage reduction strategy for sub-70 nm memory circuit in implementation of high performance circuits. In Proceedings of the IEEE dallas/CAS workshop (pp. 145–148) Texas.

Razavipour, G., Afzali-Kusha, A., & Pedram, M. (2009). Design and analysis of two low-power SRAM cell structures. IEEE Transactions on Very Large Scale Integration Systems, 10(17), 1551–1555.

Pasendiand, G., & Fakhraie, S. M. (2014). An 8T low voltage and low leakage half selection disturb free SRAM using Bulk-CMOS and FinFETs. IEEE Transactions Electron Devices, 7(61), 2357–2363.

Pavlov, A., Sachdev, M., & Pineda de Gyvez, J. (2004). An SRAM weak cell fault model and a DFT technique with a programmable detection threshold. In Proceedings of ITC international test conference (pp. 1006–1015).

Srivastava, A., & Zang, C. (2008). An adaptive body bias generator for low voltage CMOS VLSI circuits. International Journal of Distributed Sensor Networks, 4, 213–222.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lorenzo, R., Chaudhury, S. A Novel SRAM Cell Design with a Body-Bias Controller Circuit for Low Leakage, High Speed and Improved Stability. Wireless Pers Commun 94, 3513–3529 (2017). https://doi.org/10.1007/s11277-016-3788-5

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-016-3788-5