Abstract

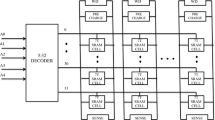

Technology scaling facilitates to meet ever increasing demands for a portable and battery operated systems, at the same time causes diminution of length of the channel, gate oxide layer and threshold voltage which increases the leakage or static power at a standby mode. Static or leakage power is the dominating factor of total power dissipation in deep nanometer technologies below 90 nm. In memory design, parameters such as power, delay and stability of the memory are considered for which affects the performance of the memory. Static random access memory (SRAM) is a type of RAM, which does not need to be refreshed periodically and data is not written permanently in it. This manuscript dedicates in designing 256 × 4 memory array structure using imminent SRAM cell and sense amplifier for usage as cache memories in most modern computer systems. The other sustaining devices in executing this array structure are row decoder, column decoder and control unit. Design metrics such as static power, dynamic power, delay, power delay product, energy, energy delay product, rise time, fall time and slew rate are taken into account. All the circuits were designed using SYNOPSYS EDA tool and simulated in 30 nm technology. Simulation results shows that array structure designed using proposed SRAM cell and sense amplifier provides better performance than existing array structure.

Similar content being viewed by others

References

Moghaddam, M., & Timarchi, S. (2016). An ultra low power 9T SRAM cell based on threshold voltage techniques. Circuits, Systems and Signal Processing, 35, 1437–1455.

Lorenzo, R., & Chaudhury, S. (2017). Dynamic threshold sleep transistor technquie for high speed and low leakage in CMOS circuits. Circuits Syst Signal Process, 36, 2654–2671.

Gavaskar, K., & Ragupathy, U. S. (2018). Low power self-controllable voltage level and low swing logic based 11T SRAM cell for high speed CMOS circuits. Analog Integrated Circuits and Signal Processing, 1–17, https://doi.org/10.1007/s10470-018-1277-3.

Liang, C. Y., & Kuang, S. R. (2018). A low power codeword based Viterbi Decoder with fine grained error detection and correction techniques. Arabian Journal for Science and Engineering, 43, 585–595.

Kumar, S., & Singh, C. (2016). Study of voltage and current sense amplifier. International Journal of Recent Trends in Engineering and Research, 2, 512–518.

Kim, J. P., & Kang, S. H. (2017). Offset cancelling current sampling sense amplifier for resistive non volatile memory in 65 nm CMOS. IEEE Journal of Solid State Circuits, 52(2), 496–504.

Ajaz, S., & Le, H. (2017). High throughput partial parallel block layered decoding architecture for non binary LDPC codes. Integration the VLSI Journal, 59, 52–63.

Lorenzo, R., & Chaudhury, S. (2016). Review of circuit level leakage minimization techniques in CMOS VLSI circuits. IETE Technical Review., 34, 165–187.

Gavaskar, K., & Priya, S. (2013). Design of efficient low power stable 4-bit memory cell. International Journal of Computer Applications, 84(1), 0975–8887.

Gavaskar, K., & Ragupathy, U. S. (2017). An efficient design and analysis of low power SRAM memory cell for ULTRA applications. Asian Journal of Research in Social Sciences and Humanities, 7(1), 962–975.

Kim, J., & Mazumder, P. (2017). A robust 12T SRAM cell with improved write marign for ultra-low power applications in 40 nm CMOS. Integration the VLSI Journal, 57, 1–10.

Jiao, H., & Kursun, V. (2016). Variability-aware 7T SRAM circuit with low leakage high data stability SLEEP mode. Integration the VLSI Journal., 53, 68–79.

Lorenzo, R., & Chaudhury, S. (2017). A Novel SRAM cell design with a body-bias controller circuit for low leakage, high speed and improved stability. Wireless Personal Communications, 94, 3513–3529.

Lorenzo, R., & Chaudhury, S. (2017). Novel 9T SRAM architecture for low leakage and high performance. Analog Integrated Circuits and Signal Processing, 92(2), 315–325.

Lorenzo, R., & Chaudhury, S. (2017). LCNT- an approach to reduce leakage power in CMOS integrated circuits. Microsystem Technologies, 23(9), 4245–4253.

Nayak, D., & Mahapatra, K. (2017). Current starving the SRAM cell: A strategy to improve cell stability and power. Circuits, Systems and Signal Processing, 36, 3047–3070.

Sulek, W. (2016). Non binary LDPC decoders design for maximizing throughput of FPGA implementation. Circuits, Systems and Signal Processing, 35, 4060–4080.

Singh, S., & Akashe, S. (2017). Low power consuming 1 KB (32 × 32) memory array using compact 7T SRAM cell. Wireless Personal Communications, 96, 1099–1109.

Chandrasetty, V. A., & Aziz, S. M. (2015). Resource efficient LDPC decoder for multimedia communication. Integration the VLSI Journal, 48, 213–220.

Singh, P., & Arun, V. (2016). Design and analysis of all optical half adder, half subractor and 4 bit decoder based on SOA-MZI configuration. Optical and Quantum Electronics, 48, 159–172.

Tejeswar, M., & Brundavani, P. (2015). Low static and dynamic power MTCMOS based 12T SRAM cell with recovery boosting. International Journal of Innovative Research in Computer and Communication Engineering, 4, 133–141.

Tiwari, N., & Atre, P. (2017). Highly robust asymmetrical 9T SRAM with trimode MTCMOS technique. Microsystem Technologies, 25(5), 1593–1598.

Gavaskar, K., & Ragupathy, U. S. (2014). An efficient design and comparative analysis of low power memory cell structures. In IEEE international conference on green computing, communication and electrical engineering (ICGCCEE’14) (pp. 489–493).

Upadhyay, P., & Mandal, D. (2014). A design of low swing and multi threshold voltage based low power 12T SRAM cell. Computer and Electrical Engineering, 45, 108–121.

Kumar, R., & Yadav, A. (2015). Low power design techniques for reduction of leakage power in CMOS VLSI circuits using modified sleepy keeper. International Journal of Electronics and Communication Technology, 4, 52–61.

Sathia Priya, M., & Joy, B. (2015). Design of SRAM cell by using self controllable voltage level circuits. International Journal of Innovative Research in Computer and Communication Engineering, 3, 708–714.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gavaskar, K., Ragupathy, U.S. & Malini, V. Proposed Design of 1 KB Memory Array Structure for Cache Memories. Wireless Pers Commun 109, 823–847 (2019). https://doi.org/10.1007/s11277-019-06593-7

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-019-06593-7