Abstract

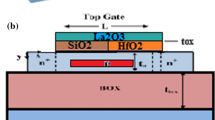

In this study, Trigate Junctionless FET device has been explored for its analog performance. The anolog and RF parameters for device performance like trans-conductance (gm), output conductance (gd), intrinsic gain (Av) and cut-off frequency (ft) are evaluated using visual TCAD tool. Simulation result reveals that a very low capacitance value (in the order of \(10^-19\)) which minimises ON state delay and making the device suitable for fast switching applications. The AC analysis of device demonstrates quite high cut off frequency of 2.44 GHz and a remarkable transconductance (Gm) of 0.154 \(\mu\)S. Furthermore, a novel CMOS Inverter has been designed using TGJLFET device structure in NMOS and PMOS configuration. The DC and transient response of the same has been studied extensively.

Similar content being viewed by others

References

Baruah, R. K., & Paily, R. P. (2015). The effect of high-k gate dielectrics on device and circuit performances of a junctionless transistor. Journal of Computational Electronics, 14(2), 492–499.

Barraud, S., Lapras, V., Previtali B., Samson MP., Lacord J., Martinie S., & Ernst, T. (2017). Performance and design considerations for gate-all-around stacked-NanoWires FETs. In 2017 IEEE international electron devices meeting (IEDM).

Young et al., C.D. (2011). Critical discussion on (100) and (110) orientation dependent transport: nMOS Planar and FinFET. In 2011 symposium on VLSI technology digest of technical papers.

Entner, R., Gehring, A., Grasser, T., & Selberherr, S. (2004). A comparison of quantum correction models for the three-dimensional simulation of FinFET structures. In 27th international spring seminar on electronics technology: Meeting the challenges of electronics technology progress.

Jeong, E.-Y., et al. (2015). Investigation of RC parasitics considering Middle-of-the-Line in Si-Bulk FinFETs for Sub-14-nm node logic applications. IEEE Transactions on Electron Devices, 62(10), 3441.

Francisco, G., et al. (2008). Anisotropy of electron mobility in arbitrarily oriented FinFETs. In ESSDERC 2007—37th European solid state device research conference.

Han, K., Qiao, G., Deng, Z., & Zhang, Y. (2017). Asymmetric drain extension Dual-kk Trigate Underlap FinFET Based on RF/Analog Circuit. Micro Machines, 8(11), 330.

Yoon, J.-S., et al. (2016). Process-induced variations of 10-nm Node Bulk nFinFETs considering middle-of-line parasitic. IEEE Transactions on Electron Devices, 63(9), 3399.

Je, M., Han, J., Shin, H., & Lee, K. (2003). A simple four-terminal small signal model of RF MOSFETs and its parameter extraction. Microelectronics Reliability, 43(4), 601–609.

Yoon, J.-S., et al. (2017). Performance and variations induced by single interface trap of Nanowire FETs at 7-nm Node. IEEE Transactions on Electron Devices, 64(2), 339.

Kaur, N., Rattan, M., & Gill, S. S. (2018). Design and optimization of novel shaped FinFET. Arabian Journal for Science and Engineering, 44(4), 3101–3116.

Loubet, N., Hook, T., Montanini, P., Yeung, CW., Kanakasabapathy, S., Guillom, M., & Wang, J. (2017). Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In 2017 symposium on VLSI technology.

Yoon, J. S., Jeong, J., Lee, S., & Baek, R. H. (2018). Multi- Vth strategies of 7-nm node nanosheet FETs With limited nanosheet spacing. IEEE Journal of the Electron Devices Society, 6, 861–865.

Genius, 3-D Device Simulator, (2019). Version 1.9.3-18, Reference Manual, Cogenda Pvt. Ltd., Singapore.

International Technology Roadmap for Semiconductors, https://en.wikipedia.org/wiki, (2018).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Prasad, M., Mahadevaswamy, U.B. Quantum Mechanical Effect on Trigate Junctionless FET for Fast Switching Application. Wireless Pers Commun 117, 1645–1657 (2021). https://doi.org/10.1007/s11277-020-07939-2

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-020-07939-2