Abstract

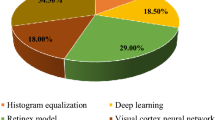

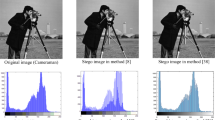

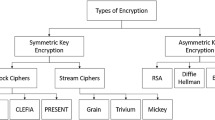

Over the last few years, the computer vision has a huge impact in the field of information technology. The foundation for computer vision is laid by image processing. Digital Image Processing is one of the vast area of research; with three indispensable aspects as; Image De-noising, Image Compression & Image Security; with multiple applications in the field of automotive, medical, space, security systems, military & many more. This survey paper includes the evolutionary analysis of various image de-nosing techniques such as Median filtering, Pixel similarity weighted frame averaging, Gaussian filtering, Bilateral filtering, Anisotropic diffusion; that are used for betterment of system performance in terms of noise suppression, edge preservation, texture detection, Operating frequency, PSNR & many more. Moreover, the paper also includes the evolutionary analysis of multiple image compression techniques based on DCT, DWT, fractal image compression & neural network. Finally, the various image security techniques are analyzed. From the study of various literatures on image processing, it is found that combine model of image processing with all the three stages including image de-noising followed by image compression & image security is not yet discussed.

Similar content being viewed by others

References

Li, C., Balla-Arabé, S., & Yang, F. (2016). Embedded multi-spectral image processing for real-time medical application. Journal of Systems Architecture, 64, 26–36.

Lahmiri, S. (2017). An iterative denoising system based on Wiener filtering with application to biomedical images. Optics & Laser Technology, 90, 128–132.

Taher, F., Zaki, A., & Elsimary, H. (2016, October). Design of low power FPGA architecture of image unit for space applications. In 2016 IEEE 59th international Midwest symposium on circuits and systems (MWSCAS) (pp. 1–4). IEEE.

Schwiegelshohn, F., Gierke, L., & Hübner, M. (2015, June). FPGA based traffic sign detection for automotive camera systems. In 2015 10th international symposium on reconfigurable communication-centric systems-on-chip (ReCoSoC) (pp. 1–6). IEEE.

HosseinKhani, Z., Hajabdollahi, M., Karimi, N., Soroushmehr, R., Shirani, S., Najarian, K., & Samavi, S. (2018). Adaptive real-time removal of impulse noise in medical images. Journal of Medical Systems, 42(11), 1–9.

Jelodari, P. T., Kordasiabi, M. P., Sheikhaei, S., & Forouzandeh, B. (2019). FPGA implementation of an adaptive window size image impulse noise suppression system. Journal of Real-Time Image Processing, 16(6), 2015–2026.

Tan, X., Liu, Y., Zuo, C., & Zhang, M. (2017). A real-time video denoising algorithm with FPGA implementation for Poisson–Gaussian noise. Journal of Real-Time Image Processing, 13(2), 327–343.

Gabiger-Rose, A., Kube, M., Weigel, R., & Rose, R. (2013). An FPGA-based fully synchronized design of a bilateral filter for real-time image denoising. IEEE Transactions on Industrial Electronics, 61(8), 4093–4104.

Dabhade, S. D., Rathna, G. N., & Chaudhury, K. N. (2017). A reconfigurable and scalable FPGA architecture for bilateral filtering. IEEE Transactions on Industrial Electronics, 65(2), 1459–1469.

Pal, C., Kotal, A., Samanta, A., Chakrabarti, A., & Ghosh, R. (2016). An efficient FPGA implementation of optimized anisotropic diffusion filtering of images. International Journal of Reconfigurable Computing, 2016, 3020473.

Fredj, A. H., Abdallah, M. B., Malek, J., & Azar, A. T. (2016). Fundus image denoising using FPGA hardware architecture. International Journal of Computer Applications in Technology, 54(1), 1–13.

Castellano, G., De Caro, D., Esposito, D., Bifulco, P., Napoli, E., & PetraAndreozziCesarelliStrollo, N. E. M. A. G. (2019). An FPGA-oriented Algorithm for real-time filtering of poisson noise in video streams, with application to X-ray fluoroscopy. Circuits, Systems, and Signal Processing, 38(7), 3269–3294.

Genovese, M., & Napoli, E. (2013). FPGA-based architecture for real time segmentation and denoising of HD video. Journal of Real-Time Image Processing, 8(4), 389–401.

Licciardo, G. D., Cappetta, C., & Di Benedetto, L. (2018). Design of a Gabor filter HW accelerator for applications in medical imaging. IEEE Transactions on Components, Packaging and Manufacturing Technology, 8(7), 1187–1194.

Licciardo, G. D., Cappetta, C., Di Benedetto, L., & Vigliar, M. (2016). Weighted partitioning for fast multiplierless multiple-constant convolution circuit. IEEE Transactions on Circuits and Systems II: Express Briefs, 64(1), 66–70.

Venkatachalam, S., & Ko, S. B. (2017). Design of power and area efficient approximate multipliers. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 25(5), 1782–1786.

Jridi, M., Alfalou, A., & Kumar Meher, P. (2012). Optimized architecture using a novel subexpression elimination on Loeffler algorithm for DCT-based image compression. VLSI Design.

Mert, Y. M. (2015, May). FPGA-based JPEG-LS encoder for onboard real-time lossless image compression. In Satellite data compression, communications, and processing XI (Vol. 9501, p. 950106). International Society for Optics and Photonics.

Kim, H., No, A., & Lee, H. J. (2018). SPIHT algorithm with adaptive selection of compression ratio depending on DWT coefficients. IEEE Transactions on Multimedia, 20(12), 3200–3211.

Huang, Z., Zhang, X., Chen, L., Zhu, Y., An, F., Wang, H., & Feng, S. (2017). A vector-quantization compression circuit with on-chip learning ability for high-speed image sensor. IEEE Access, 5, 22132–22143.

Saad, A. H., & Abdullah, M. Z. (2016). High-speed implementation of fractal image compression in low cost FPGA. Microprocessors and Microsystems, 47, 429–440.

Panigrahy, M., Chakrabarti, I., & Dhar, A. S. (2016). Low-delay parallel architecture for fractal image compression. Circuits, Systems, and Signal Processing, 35(3), 897–917.

Saad, A. M. H., & Abdullah, M. Z. (2018). High-Speed Fractal Image Compression Featuring Deep Data Pipelining Strategy. IEEE Access, 6, 71389–71403.

Tellez, D., Litjens, G., van der Laak, J., & Ciompi, F. (2019). Neural image compression for gigapixel histopathology image analysis. IEEE Transactions on Pattern Analysis and Machine Intelligence.

Ramalingam, B., Rengarajan, A., & Rayappan, J. B. B. (2017). Hybrid image crypto system for secure image communication–A VLSI approach. Microprocessors and Microsystems, 50, 1–13.

Kishore, B., Kumar, B. S., & Patil, C. R. (2015). FPGA based simple and fast JPEG encryptor. Journal of Real-Time Image Processing, 10(3), 551–559.

Altigani, A., Hasan, S., Barry, B., Naserelden, S., Elsadig, M. A., & Elshoush, H. T. (2021). A Polymorphic Advanced Encryption Standard–A Novel Approach. IEEE Access, 9, 20191–20207.

Masoumi, M., & Rezayati, M. H. (2014). Novel approach to protect advanced encryption standard algorithm implementation against differential electromagnetic and power analysis. IEEE Transactions on Information Forensics and Security, 10(2), 256–265.

Langenberg, B., Pham, H., & Steinwandt, R. (2020). Reducing the cost of implementing the advanced encryption standard as a quantum circuit. IEEE Transactions on Quantum Engineering, 1, 1–12.

Amento-Adelmann, B., Grassl, M., Langenberg, B., Liu, Y. K., Schoute, E., & Steinwandt, R. (2018). Quantum cryptanalysis of block ciphers: A case study. In Poster at Quantum Information Processing QIP, 2018.

Almazrooie, M., Samsudin, A., Abdullah, R., & Mutter, K. N. (2018). Quantum reversible circuit of AES-128. Quantum Information Processing, 17(5), 1–30.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shelke, S.K., Sinha, S.K. & Patel, G.S. Study of End to End Image Processing System Including Image De-noising, Image Compression & Image Security. Wireless Pers Commun 121, 209–220 (2021). https://doi.org/10.1007/s11277-021-08631-9

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-021-08631-9