Abstract

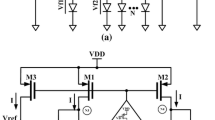

The paper presents a novel high-order temperature-compensated subthreshold voltage reference that utilizes temperature characteristics of the gate-to-source voltage of subthreshold MOS transistor. The proposed high-order temperature-compensated voltage reference has been designed using two CMOS voltage references and a current subtraction circuit to achieve a low temperature coefficient over a wide temperature range. The proposed circuit offers an output reference voltage of 250.8 mV, line sensitivity of 0.0674%/V and temperature coefficient of 37.4 ppm/°C for the temperature range varying from − 20 \(\mathrm{^\circ{\rm C} }\) to 140 °C at nominal conditions. The power supply rejection ratio is obtained as − 46.02 dB at a frequency of 100 Hz and − 41.91 dB at a frequency of 1 MHz. The proposed circuit shows an output noise of 1.86 \(\mathrm{\mu V}/\surd \mathrm{Hz}\) at 100 Hz and 259.72 \(\mathrm{nV}/\surd \mathrm{Hz}\) at 1 MHz. The proposed circuit has been designed in BSIM3V3 180 nm CMOS technology using Cadence tool. The corner analysis of the proposed circuit has also been performed to show its performance in extreme conditions. The proposed circuit occupies a small chip area of 51 \(\upmu\)m × 75.3 \(\upmu\)m.

Similar content being viewed by others

Availability of data and material

Not applicable.

Code availability

Not applicable.

References

Ueno, K., Hirose, T., Asai, T., & Amemiya, Y. (2010). A 1-mW 600-ppm/°C current reference circuit consisting of subthreshold CMOS circuits. IEEE Transactions on Circuits and Systems II: Express Briefs, 57(9), 681–685.

Fayomi, C. J. B., Wirth, G. I., Achigui, H. F., & Matsuzawa, A. (2010). Sub-1-V CMOS bandgap reference design techniques: A survey. Analog Integrated Circuits Signal Process, 62(2), 141–157.

Thakur, A., Pandey, R., & Rai, S. K. (2021). A low supply voltage, low line sensitivity, and high PSRR subthreshold CMOS voltage reference. Journal of Circuits, Systems, and Computers, 30, 2150227.

Basyurt, P. B., Bonizzoni, E., Aksin, D. Y., & Maloberti, F. (2015). Voltage reference architectures for low-supply-voltage low-power applications. Microelectronics Journal, 46(11), 1012–1019.

Souliotis, G., Plessas, F., & Vlassis, S. (2018). A high accuracy voltage reference generator. Microelectronics Journal, 75, 61–67.

Nagulapalli, R., Hayatleh, K., Barker, S., Tammam, A. A., Georgiou, P., & Lidgey, F. J. (2019). A 055 V bandgap reference with a 59 ppm/°C temperature coefficient. Journal of Circuits, Systems, and Computers, 28(7):1–12 (19501202)

Tsitouras, A., & Sotiriadis, P. P. (2019). Design of a sub-1V CMOS reference voltage generator. Microelectronics Journal, 91, 92–99.

Koh, S. K., & Lee L., (2014). Low power CMOS bandgap reference circuit. IEEE Student Conference on Research and Development, Batu Ferringhi, 1–5.

Sanborn, K., Ma, D., & Ivanov, V. (2007). A sub-1-V low-noise bandgap voltage reference. IEEE Journal of Solid-State Circuits, 42(11), 2466–2481.

Luo, H., Han, Y., Cheung, R. C. C., Liang, G., & Zhu, D. (2012). Subthreshold CMOS voltage reference circuit with body bias compensation for process variation. IET Circuits, Devices & Systems, 6(3), 198–203.

Wang, L., Zhan, C., Tang, J., et al. (2017). Analysis and design of a current-mode bandgap reference with high power supply ripple rejection. Microelectronics Journal, 68, 7–13.

Song, B. S., & Gray, P. R. (1983). A precision curvature-compensated CMOS bandgap reference. IEEE Journal of Solid-State Circuits, 18(6), 634–643.

Zhou, Z. K., Oua, X. C., Shi, Y., Zhu, P. S., Ma, Y. Q., Qiu, S., et al. (2012). A 3.2 ppm/°C curvature-compensated bandgap reference with wide supply voltage range. Microelectronics Journal, 43(11), 863–868.

Shi, Y., Li, S., Cao, J., Zhou, Z., & Ling, W. (2020). A 180 nm self-biased bandgap reference with high PSRR enhancement. Nanoscale Research Letters, 15, 1254.

Jiang, Y., & Lee, E. K. F. (2000). Design of low-voltage bandgap reference using transimpedance amplifier. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 47(6), 552–555.

Dai, Y., Comer, D. T., Comer, D. J., & Petrie, C. S. (2004). Threshold voltage based CMOS voltage reference. IEEE Proceedings of Circuits, Devices & Systems, 151(1), 58–62.

Song, H.-J., & Kim, C. K. (1993). A temperature-stabilized SOI voltage reference based on threshold voltage difference between enhancement and depletion NMOSFET’s. IEEE Journal of Solid-State Circuits, 28(6), 671–677.

Magnelli, L., Crupi, F., Corsonello, P., Pace, C., & Iannaccone, G. (2011). A 2.6 nW, 0.45 V temperature-compensated subthreshold CMOS voltage reference. IEEE Journal of Solid-State Circuits, 46(2), 465–474.

Huang, P. H., Lin, H., & Lin, Y. T. (2006). A simple subthreshold CMOS voltage reference circuit with channel-length modulation compensation. IEEE Transactions on Circuits and Systems II: Express Briefs, 53(9), 882–885.

Giustolisi, G., Palumbo, G., Criscione, M., & Cutrì, F. (2003). A low-voltage low-power voltage reference based on subthreshold MOSFETs. IEEE Journal of Solid-State Circuits, 38(1), 151–154.

Albano, D., Crupi, F., Cucchi, F., & Iannaccone, G. (2013). A pico-power temperature-compensated, subthreshold CMOS voltage reference. Int J. Circ Theory Appl., 46, 1306–1318.

Mohammed, M., Abugharbieha, K., Abdelfattah, M., & Kawar, S. (2016). Design methodology for MOSFET based voltage reference circuit implemented in 28 nm CMOS technology. AEU- International Journal of Electronics and Communications, 70(5), 568–577.

Parisia, A., Finocchiarob, A., & Palmisano, G. (2017). An accurate 1-V threshold voltage reference for ultra-low power applications. Microelectronics Journal, 63, 155–159.

Liang, Y., & Zhu, Z. (2018). A 42 ppm/°C 07 V 4.7 nW low-complexity all-MOSFET sub-threshold voltage reference. Journal of Circuits, Systems, and Computers, 27(7), 1850105.

Wang, L., Zhan, C., Tang, J., & Li, G. (2018). An amplifier offset-insensitive and high PSRR subthreshold CMOS voltage reference. Int J. Circ Theory Appl., 46(2), 259–271.

Olivera, F., & Petraglia, A. (2020). Adjustable output CMOS voltage reference design. IEEE Transactions on Circuits and Systems II: Express Briefs, 67(10), 1690–1694.

Rincon-Mora, G. A. (2002). Voltage References: From Diodes to Precision High-Order Bandgap Circuits. Wiley-IEEE Press.

Razavi, B. (2002). Design of Analog CMOS Integrated Circuits. McGraw-Hill Education.

Oliveira, A. C., Cordova, D., Klimach, H., & Bampi, S. (2017). Picowatt, 0.45–0.6 V self-biased subthreshold CMOS voltage reference. IEEE Transactions on Circuits and Systems I, 64(12), 3036–3045.

Oliveira, A. C., Cordova, D., Bampi, S., & Klimach, H. (2018). A 0.12–0.4 V, versatile 3-transistor CMOS voltage reference for ultra-low power systems. IEEE Transactions on Circuits and Systems I, 65, 3790–3799.

Yousefi, S., & Jalali, M. (2016). A high-PSRR low-power CMOS voltage reference based on weighted VGS difference. AEU—International Journal of Electronics and Communications, 70(1), 50–57.

Liang, C., Chung, C., & Lin, H. (2010). A low-voltage band-gap reference circuit with second-order analyses. International Journal of Circuit Theory and Applications, 39(12), 1247–1256.

Osaki, Y., Hirose, T., Kuroki, N., & Numa, M. (2013). 1.2-V supply, 100-nW, 1.09-V bandgap and 0.7-V supply, 52.5-nW, 0.55-V subbandgap reference circuits for nanowatt CMOS LSIs. IEEE Journal of Solid-State Circuits, 48(6), 1530–1538.

Duan, Q., & Roh, J. (2015). A 1.2-V 4.2 ppm/°C high-order curvature-compensated CMOS bandgap reference. IEEE Transactions on Circuits and Systems I, 62(3), 662–670.

Lee, K. K., Lande, T. S., & Häfliger, P. T. (2015). A sub-μW bandgap reference circuit with an inherent curvature-compensation property. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(1), 1–9.

Funding

Not applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

All authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Thakur, A., Pandey, R. & Rai, S.K. A High-Order Temperature-Compensated Subthreshold Voltage Reference Using Channel Length Modulation Compensation Technique. Wireless Pers Commun 126, 263–284 (2022). https://doi.org/10.1007/s11277-022-09744-5

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-022-09744-5