Abstract

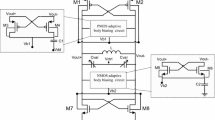

This paper proposed to design a CMOS based LC-voltage control oscillator using substrate bias effect and low-voltage folded-cascode current mirror circuit using an LC tank circuit at 2.5 GHz oscillation Frequency. The paper delves into the substrate-biasing technique, which adjusts the threshold voltage of a CMOS transistor, and the low-voltage folded-cascode current mirror circuit that utilizes CMOS technology to improve the performance of the current mirror circuit. The folded-cascode current mirror circuit comprises of a cascode structure in the input stage and a folded structure in the output stage, which is used to increase the output impedance and provide a more stable output current. The paper concludes that the folded-cascode current mirror circuit is a powerful tool in CMOS circuit design, offering improved performance and accuracy over the traditional current mirror circuit. In this simulation is carried out through cadence virtuoso generic process design kit (GPDK) with 90 nm technology. The simulation results exhibits phase noise of − 154.92 dBc/Hz @ 1 MHz, low power consumption of 4.8mW and the Figure of Merit − 216.09 dBc/Hz at 2.5 GHz oscillation frequency.

Similar content being viewed by others

Data Availability Statement

All the data is collected from the simulation reports of the software and tools used by the authors. Authors are working on implementing the same using real world data with appropriate permissions.

References

Wang, X., et al. (2016). 2.4-GHzBand low-voltage LC-VCO IC with simplified noise filtering in 180-nm CMOS. In 2016 IEEE MTT-S international wireless symposium (IWS).

Ellaithy, D. M. (2023). Voltage-controlled oscillator based analog-to-digital converter in 130-nm CMOS for biomedical applications. Journal of Electrical Systems and Information Technology, 10(1), 38.

Pillay, S., & Srivastava, V. (2023). Design of an active-loaded differential voltage-controlled oscillator (VCO) using double-gate MOSFET. International Journal of Engineering Trends and Technology, 71(12), 248–263.

Kaipu, S. V. R., Vaish, K., Komatireddy, S., Sood, A., & Goswami, M. (2016). Design of a low power wide range phase locked loop using 180nm CMOS technology. In 2016 international conference on signal processing and communication (ICSC) (pp. 443-447). IEEE.

Esmaeilzadeh, M., Audet, Y., Ali, M., & Sawan, M. (2022). A low-phase-noise CMOS ring voltage-controlled oscillator intended for time-based sensor interfaces. IEEE Access, 10, 101186–101197.

Prasad, N., Gamad, R. S., & Kushwah, C. B. (2009). Design of a 22–40 GHz low phase noise and low power LC VCO. IJCNS International Journal of Computer and Network Security, 1(3), 15–18.

Prasad, N., et al. (2011). Layout design of LC VCO with current mirror using 0.18 µm technology. Wireless Engineering and Technology, 2(2), 102–106.

Hsu, M. T., Chen, P. H., & Lee, Y. Y. (2014). Design of 5 GHz low-power CMOS LC VCO based on complementary cross-coupled topology with modified tail current-shaping technique. International Journal of Microwave and Wireless Technologies, 6(6), 573–580.

Azadmousavi, T., Aghdam, E. N., & Frounchi, J. (2018). A low power current-reuse LC-VCO with self body-bias schema. In Iranian conference on electrical engineering (ICEE), (pp. 294–299). IEEE.

Moon, Y.-J., et al. (2009). A 4.39–5.26 GHz LC-tank CMOS voltage-controlled oscillator with small VCO-gain variation. IEEE Micorwave and Wireless Components Letters, 19(8), 524–526.

Peiming, L., Shizhen, H., Lianyi, S., & Run, C. (2009). Design of a 2GHz low phase noise LC VCO. In Proceedings of the international multiconference of engineers and computer scientists (Vol. 2, pp. 18-20).

Plouchart, J. O., Ferriss, M., Sadhu, B., Sanduleanu, M., Parker, B., & Reynolds, S. (2013). A 73.9–83.5 GHz synthesizer with− 111dBc/Hz phase noise at 10MHz offset in a 130nm SiGe BiCMOS technology. In 2013 IEEE radio frequency integrated circuits symposium (RFIC) (pp. 123–126). IEEE.

Cheng, K. H., Hung, C. L., Gong, C. S. A., Liu, J. C., Jiang, B. Q., & Sun, S. Y. (2014). A 0.9-to 8-GHz VCO with a differential active inductor for multistandard wireline SerDes. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(8), 559–563.

Thakore, K. P., Shah, D. J., & Devashrey, N. M. (2022). Recent trends in LC voltage controlled oscillator to achieve low phase noise: A literature survey. Grenze International Journal of Engineering & Technology (GIJET), 8(1).

Rajpoot, P., Gurjar, R. C., & Gamad, R. S. (2019). Low phase noise wide tuning range LC oscillator for RF application using varactor bank. Journal of Telecommunication, Electronic and Computer Engineering JTEC, 11(3), 31–36.

Nandini, V. V. (2021). Performance characterization for high frequency CMOS voltage control ring oscillators. In Journal of Physics: Conference Series (Vol. 1804, No. 1, p. 012180). IOP Publishing.

Author information

Authors and Affiliations

Contributions

N. Suresh: He performed the conceptualization, Methodology, Data collection and writing the study. S. Ashok Kumar: He analysis the datazset and conceptualization in the study. Harikrishna Kamatham: He Performed the Analysis the overall concept, writing and editing. He also analysis the paper and supervisor of this paper.

Corresponding author

Ethics declarations

Conflict of Interest

The authors declare that we have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Suresh, N., Kumar, S.A. & Kamatham, H. Design of CMOS Based LC-Voltage Control Oscillator Using Substrate Bias Effect and Current Mirror Technique. Wireless Pers Commun 138, 1351–1362 (2024). https://doi.org/10.1007/s11277-024-11567-5

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-024-11567-5