Abstract

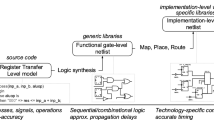

VLSI testing is being pushed to the high-level based technology. In this paper a Verilog Register transfer level Model (VRM) for integrated circuits is proposed. The model provides a text format file, which is convenient and more practical for developing succeeding Register Transfer Level (RTL) test tools, such as fault simulation, test pattern generation and so forth. Based on the VRM, an RTL concurrent fault simulation approach is presented. After RTL fault models and super faults defined, the concurrent fault simulation algorithm is given. The corresponding RTL concurrent fault simulator, VFSim, was implemented. The initial experiments show that the RTL fault simulator is efficient for VLSI circuits.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.References

Fallah F, Ashar P, Devadas S. Simulation vector generation from HDL descriptions for observability-enhanced statement coverage. In Proc. Design Automation Conf., June 1999, pp.666–671.

F Corno, M Sonza Reorda, G Squillero. RT-level ITC’99 benchmarks and first ATPR results. IEEE Design & Test of Computer, July-August 2000, pp.44–53.

Levendel Y H, Menon P R. Test generation for computer hardware description language. IEEE Trans. Computers, July 1982, C-31(7): 577–588.

Murray B T, Hayes J P. Hierarchical test generation using pre-computed tests for modules. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, June 1990, 9(6): 594–603.

Roy K, Abraham J A. High-level test generation using data flow descriptions. In Proc. Eur. Conf. Design Automation, Mar. 1990, pp.480–484.

Ferrandi F, Fummi F, Sciuto D. Implicit test generation for behavioral VHDL model. In Proc. Int. Test Conference, Oct. 1998, pp.587–596.

Bhatia S, Jha N K. Integration of hierarchical test generation with behavioral synthesis of controller and data path circuits. IEEE Trans. VLSI Systems, Dec. 1998, 6(4): 608–619.

Ghosh I, Fujita M. Automatic test generation for functional register-transfer level circuits using assignment decision diagrams. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, March 2001, 20(3): 402–415.

Williams S. The ICARUS Verilog compilation system. http://icarus.com/eda/verilog

F Corno, G Cumani, M Sonza Reorda, G Squillero. RT-level fault simulation techniques based on simulation command scripts. In XV Conf. Design of Circuits and Integrated Systems, Le Corum, Montpellier, Nov. 21-24, 2000, pp.825–830.

Breuer M A, Friedman A D. Diagnosis & Reliable Design of Digital Systems. Computer Science Press, USA, 1976.

Niermann M, Cheng W T, Patel J H. PROOFS: A fast, memory-efficient sequential circuit fault simulator. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, Feb. 1992, 11(2): 198–207.

Lee H K, Ha D S. HOPE: An efficient parallel fault simulator for synchronous sequential circuits. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, Feb. 1996, 15(9): 1048–1058.

Reorda M S, Corno F, Squillero G. ITC’99 benchmarks. http://www.cad.polito.it/tools/itc99.html.

CMU Lower Power Group. CMU-DSP Benchmarks. http://www.ece.cmu.edu/∼lowpower/benchmarks.html

Bhasker J. A Verilog HDL Primer (Second Edition). Star Galaxy Publishing, USA, 1999.

Yinghua Min. Why RTL ATPG. Journal of Computer Science and Technology, 2002, 17(2): 113–117.

Thaker P A, Agrawal V D, Zaghloul M E. A test evaluation technique for vlsi circuits using register-transfer level fault modeling. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, Aug. 2003, 22(8): 1104–1113.

Yin Z, Min Y, Li X. An approach to RTL fault extraction and test generation. In Proc. 10th Asian Test Symposium, 2001, pp. 219–224.

Author information

Authors and Affiliations

Corresponding author

Additional information

This work was supported by the National High-Technology Development 863 Program of China under Grant No.2001AA111100. This paper is based on two preliminary papers presented at the IEEE 4th Workshop on RTL and High Level Testing, (WRTLT’03).

Li Shen was born in 1937. He graduated from the Department of Electrical Engineering, Zhejiang University, China, in 1959. Since then, he joined the staff of Institute of Computing Technology, Chinese Academy of Sciences, Beijing, where he is currently a professor. He is now an IEEE senior member. He has been engaged in research and design of digital circuits and computers for many years. From Oct. 1982 to Sept. 1984, he was a visiting scholar at Thomas J. Watson School of Engineering, Applied Science and Technology, State University of New York at Binghamton. From Oct. 1989 to Nov. 1991, he worked at Integrix Inc., Newbury Park, California, for several cooperative projects on workstation development and ASIC design. His research interests include soft computing, ASIC design, design for testability and fault testing.

Rights and permissions

About this article

Cite this article

Shen, L. VFSim: Concurrent Fault Simulation at Register Transfer Level. J Comput Sci Technol 20, 175–186 (2005). https://doi.org/10.1007/s11390-005-0175-1

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/s11390-005-0175-1