Abstract

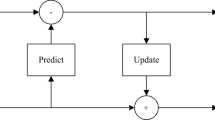

In this paper, we propose a VLSI architecture that performs the line-based discrete wavelet transform (DWT) using a lifting scheme. The architecture consists of row processors, column processors, an intermediate buffer and a control module. Row processor and Column processor work as the horizontal and vertical filters respectively. Intermediate buffer is composed of five FIFOs to store temporary results of horizontal filter. Control module schedules the output order to external memory. Compared with existing ones, the presented architecture parallelizes all levels of wavelet transform to compute multilevel DWT within one image transmission time, and uses no external but one intermediate buffer to store several line results of horizontal filtering, which decreases resource required significantly and reduces memory efficiently. This architecture is suitable for various real-time image/video applications.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.References

Daubechies I. Ten lectures on wavelets. CBMS-NSF Regional Conf. Series in Appl. Math., Vol. 61. Society for Industrial and Applied Mathematics, Philadelphia, PA, 1992.

Daubechies I, Sweldens W. Factoring wavelet transfomis into lifting steps. Technical Report., Bell Laboratories, 1996.

Sweldens W. The lifting scheme: A new philosophy in biorthogonal wavelet constructions. In Proc. SPIE, Vol. 2569, San Diego, CA, 1995, pp.68–79.

JPEG2000 part I final draft international standard (corrected and formatted). ISO/IEC JTC1/SC29 WG1 N1890, September 25, 2000.

Fridman J S, Manolakos E S. Discrete wavelet transform: Data dependence analysis and synthesis of distributed memory and control array architectures. IEEE Trans. Signal Processing, 1997, 45(5): 1291–1308.

Grzeszczak A, Mandal M K, Panchanathan S et al. VLSI implementation of discrete wavelet transform. IEEE Trans. VLSI System, 1996, 4(6): 421–433.

Chakrabarti C, Vishwanath M. Efficient realizations of the discrete and continuous wavelet transforms: From single chip implementations to mappings on SIMD array computers. IEEE Trans. Signal Processing, 1995, 43(3): 759–771.

Chrysafis C, Ortega A. Line based, reduced memory, wavelet image compression. IEEE Trans. Image Processing, 2000, 9(3): 378–389.

Andra K, Chakrabarti C, Acharya T. A VLSI architecture for lifting-based forward and inverse wavelet transform. IEEE Trans. Signal Processing, 2002, 50(4): 966–977.

Gab Cheon Jung, Duk Young Jin, Seong Mo Park. An efficient line based VLSI architecture for 2-D lifting DWT. In Proc. The 47th IEEE International Midwest Symposium on Circuits and Systems, Hiroshima, Japan, 2004, Vol.2 pp.249–252.

Dillen G, Georis B, Legat J D et al. Combined line-based architecture for the 5-3 and 9–7 wavelet transform of JPEG2000. IEEE Trans. Circuits and Systems for Video Technology, 2003, 13(9): 944–950.

Calderbank A R, Daubechies I, Sweldens W et al. Wavelet transforms that map integers to integers. Appl. Comput. Harmon. Anal., 1998, 5(7): 332–369.

Acharya T. A high speed systolic architecture for discrete wavelet transforms. In Proc. IEEE Global Telecommun. Conf., Pheonix, Az, 1997, Vol. 2, pp.669–673.

Luo Lin, Li Jin, Li Shi-Peng et al. A motion compensated lifting wavelet codec for 3D video coding. Journal of Computer Science and Technology, 2003, 18(2): 210–213.

Parhi K K, Nishitani T. VLSI architectures for discrete wavelet transform. IEEE Trans. VLSI System, 1993, 1(6): 191–202.

Author information

Authors and Affiliations

Corresponding author

Additional information

Supported by the National Natural Science Foundation of China under Grant Nos. 60532060 and 60507012.

Electronic supplementary material

Rights and permissions

About this article

Cite this article

Liu, K., Wang, KY., Li, YS. et al. A Novel VLSI Architecture for Real-Time Line-Based Wavelet Transform Using Lifting Scheme. J Comput Sci Technol 22, 661–672 (2007). https://doi.org/10.1007/s11390-007-9087-6

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11390-007-9087-6