Abstract

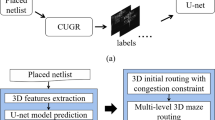

As technology advances, there is a considerable gap between the congestion model used in global routing and the routing resource consumption in detailed routing. The new factors contributing to congestion include local pin access paths, vias, and various design rules. In this paper, we propose a practical congestion model with measurement of the impact of design rules, and resources consumed by vias and local pin access paths. The model is compatible with path search algorithms commonly used in global routing. Validated by full-flow routing, this congestion model correlates better with real resource consumption situation in detailed routing, compared with previous work. It leads to better solution quality and shorter runtime of detailed routing when it is used in the layer assignment phase of global routing stage.

Similar content being viewed by others

References

Albrecht C. Global routing by new approximation algorithms for multicommodity flow. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2001, 20(5): 622–632.

Roy J A, Markov I L. High-performance routing at the nanometer scale. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2008, 27(6): 1066–1077.

Pan M, Xu Y, Zhang Y, Chu C. FastRoute: An efficient and high-quality global router. VLSI Design, 2012, 2012: Article ID 608362.

Moffitt M D. MaizeRouter: Engineering an effective global router. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2008, 27(11): 2017–2026.

Chang Y, Lee Y, Gao J, Wu P, Wang T. NTHU-Route 2.0: A robust global router for modern designs. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2010, 29(12): 1931–1944.

Hsu C, Chen H, Chang Y. Multilayer global routing with via and wire capacity considerations. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2010, 29(5): 685–696.

Taghavi T, Alpert C, Huber A, Li Z, Nam G, Ramji S. New placement prediction and mitigation techniques for local routing congestion. In Proc. IEEE/ACM International Conference on Computer-Aided Design, November 2010, pp.621-624.

Wei Y, Sze C C N, Viswanathan N, Li Z, Alpert C J, Reddy L N, Huber A D, Téllez G E, Keller D, Sapatnekar S S. GLARE: Global and local wiring aware routability evaluation. In Proc. the 49th ACM/EDAC/IEEE Design Automation Conference, June 2012, pp.768-773.

Shojaei H, Davoodi A, Linderoth J T. Planning for local net congestion in global routing. In Proc. International Symposium on Physical Design, March 2013, pp.85-92.

Lee C Y. An algorithm for path connections and its applications. IRE Transactions on Electronic Computers, 1961, EC-10(3): 346–365.

Moore E F. The shortest path through a maze. In Proc. International Symposium on the Theory of Switching, April 1957, pp.285-292.

Hart P E, Nilsson N J, Raphael B. A formal basis for the heuristic determination of minimum cost paths. IEEE Transactions on Systems Science and Cybernetics, 1968, 4(2): 100–107.

Kastner R, Bozorgzadeh E, Sarrafzadeh M. Pattern routing: Use and theory for increasing predictability and avoiding coupling. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2002, 21(7): 777–790.

Lee T, Wang T. Congestion-constrained layer assignment for via minimization in global routing. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2008, 27(9): 1643–1656.

Lee T, Wang T. Robust layer assignment for via optimization in multi-layer global routing. In Proc. International Symposium on Physical Design, March 2009, pp.159-166.

Liu W, Li Y. Negotiation-based layer assignment for via count and via overflow minimization. In Proc. the 16th Asia and South Pacific Design Automation Conference, January 2011, pp.539-544.

Cho M, Lu K, Yuan K, Pan D Z. BoxRouter 2.0: A hybrid and robust global router with layer assignment for routability. ACM Transactions on Design Automation of Electronic Systems, 2009, 14(2): Article No. 32.

Hu J, Roy J A, Markov I L. Completing high-quality global routes. In Proc. the 19th International Symposium on Physical Design, March 2010, pp.35-41.

Dai K, Liu W, Li Y. NCTU-GR: Efficient simulated evolution-based rerouting and congestion-relaxed layer assignment on 3-D global routing. IEEE Transactions on Very Large Scale Integration Systems, 2012, 20(3): 459–472.

Liu W, Kao W, Li Y, Chao K. NCTU-GR 2.0: Multithreaded collision-aware global routing with boundedlength maze routing. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2013, 32(5): 709–722.

Viswanathan N, Alpert C J, Sze C C N, Li Z, Wei Y. The DAC 2012 routability-driven placement contest and benchmark suite. In Proc. the 49th ACM/EDAC/IEEE Design Automation Conference, June 2012, pp.774-782.

Liu W, Koh C, Li Y. Case study for placement solutions in ISPD11 and DAC12 routability-driven placement contests. In Proc. ACM International Symposium on Physical Design, March 2013, pp.114-119.

Author information

Authors and Affiliations

Corresponding author

Additional information

This work was supported by the National Natural Science Foundation of China under Grant No. 61274031. A preliminary version of the paper was published in the Proceedings of CAD/Graphics 2013.

Rights and permissions

About this article

Cite this article

Qi, ZD., Cai, YC. & Zhou, Q. Design-Rule-Aware Congestion Model with Explicit Modeling of Vias and Local Pin Access Paths. J. Comput. Sci. Technol. 30, 614–628 (2015). https://doi.org/10.1007/s11390-015-1515-4

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11390-015-1515-4