Abstract

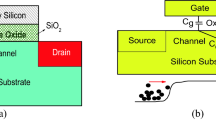

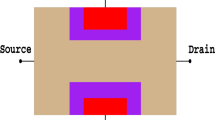

The development of next 32 nm generation and below needs innovations on not only device structures, but also fabrication techniques and material selections. Among those promising technologies, new gate structures as high-k gate dielectric and metal gate, strain channel carrier mobility enhancement technology, and novel non-planar MOSFET structures are all possible candidate technologies. In this paper, we will specify our discussion on the research progress of high-k-metal gate and non-planar MOSFET-technologies that are suitable to 32 nm technology node and beyond.

Similar content being viewed by others

References

The International Technology Roadmap for Semiconductors (ITRS) Roadmap, ITRS roadmap 2006, http://public.itrs.net, 2006

Wakabayashi H, Yamagami S, Ikezawa N, et al. Sub-10-nm planar-bulk-CMOS devices using lateral junction control. In: Int. Electron Devices Meeting (IEDM) Tech. Dig., Dec. 2003. 989–991

Kang J F, Yu H Y, Ren C, et al. Improved electrical and reliability characteristics of HfN/HfO2 gated nMOSFET with 0.95 nm EOT fabricated using a gate-first process. IEEE Elect Dev Lett, 2005, 26: 237–239

Lee S J, Rhee S J, Clark R, et al. Reliability projection and polarity dependence of TDDB for ultra thin CVD HfO2 gate dielectrics. VLSI Tech Dig, 2002, 78–79

Yu H Y, Lim H F, Chen J H, et al. Physical and electrical characteristics of HfN gate electrode for advanced MOS devices. IEEE Elect Dev Lett, 2003, 24: 230–232

Tseng H-H, Ramon M E, Hebert L, et al. ALD HfO2 using heavy water (D2O) for improved MOSFET stability. In: Int Elect Dev Meet’ 03, 2003, 83–86

Kang J F, Ren C, Yu H Y, et al. Anovel dual-metal gate integration process for sub-1 nm EOT HfO2 CMOS devices. In: 2004 International Conference on Solid State Devices and Materials (SSDM 2004), Tokyo, Japan, Sept. 15–17, 2004

Kang J F, Yu H Y, Ren C, et al. Scalability and reliability characteristics of CVD HfO2 gate dielectrics with HfN electrodes for advanced CMOS applications. J Elect Soc, 2007, 154: H927–H932

Sa N, Kang J F, Yang H, et al. Mechanism of positive-bias temperature instability in sub-1 nm TaN/HfN/HfO2 gate stack with low preexisting traps. IEEE Elect Dev Lett, 2005, 26(9): 610–612

Choi Y K, Ha D, King T J, et al. Nanoscale ultrathin body PMOSFETs with raised selective germanium source/drain. IEEE Elect Dev Lett, 2001, 22(9): 447–448

Uchida K, Koga J, Takagi S-I. Experimental study on carrier transport mechanisms in double-and single-gate ultrathin-body MOSFETs-Coulomb scattering, volume inversion, and δTSOI-induced scattering. IEEE Elect Dev Meet, 2003, 33.5.1-33.5.4

Ren Z, Hegde S, Doris B, et al. An experimental study on transport issues and electrostatics of ultrathin body SOI pMOSFETs. IEEE Elect Dev Lett, 2002, 23(10): 609–611

Tian Y, Huang R, Zhang R, et al. A novel nanoscaled device concept: Quasi-SOI MOSFET to eliminate the potential weaknesses of UTB SOI MOSFET. IEEE Trans Elect Dev, 2005, 52(4): 561–568

Tian Y, Xiao H, Huang R, et al. Quasi-SOI MOSFET — A promising bulk device candidate for extremely scaled era. IEEE Trans Elect Dev, 2007, 53(7): 1784–1788

Timp G, Bude J, Bourdelle K K, et al. The ballistic nano-transistor. IEDM Tech Dig, 1999, 55–58

Natori K. Ballistic metal-oxide-semiconductor field effect transistor. J Appl Phys, 1994, 76(8): 1029–1036

Palestri P, Esseni D, Eminente S, et al. Understanding quasi-ballistic transport in nano-MOSFETs: Part I—Scattering in the channel and in the drain. IEEE Trans Elect Dev, 2005, 52(12): 2727–2732

Eminente S, Esseni D, Palestri P, et al. Understanding quasi-ballistic transport in nano-MOSFETs: Part II—Technology scaling along the ITRS. IEEE Trans Elect Dev, 2005, 52(12): 2736–2743

Lundstrom M. Elementary scattering theory of the Si MOSFET. IEEE Elect Dev Lett, 1997, 18(7): 361–363

Xia Z L, Du G, Liu X Y, et al. Effect of surface roughness on quasi-ballistic transport in nano-scale Ge and Si double-gate MOSFETs. ICSICT, 2006

Du G, Liu X Y, Xia Z L, et al. Monte Carlo simulation of p and n channel GOI MOSFETs by solving quantum Boltzmann equation. IEEE Trans Elect Dev, 2005, 52(10): 2258–2264

Xia X L, Du G, Liu X Y, et al. Carrier effective mobilities in germanium MOSFET inversion layer investigated by Monte Carlo simulation. Solid-state Elect, 2005, 49(12): 1942–1946

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, Y., Zhang, X., Liu, X. et al. Novel devices and process for 32 nm CMOS technology and beyond. Sci. China Ser. F-Inf. Sci. 51, 743–755 (2008). https://doi.org/10.1007/s11432-008-0071-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-008-0071-8