Abstract

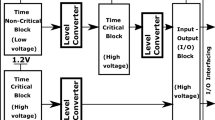

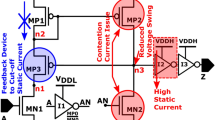

Low power on-chip interconnect technique is important for deep submicron SOC design. In this paper, a novel low swing drivers scheme based on charge redistribution is proposed. Significant reduction in power dissipation is achieved by dividing the full signal swing into several lower ones. The proposed circuits are especially suitable for driving multi-branch transmission wires by utilizing higher efficiency of charges. Compared with the reference design, the new scheme can reduce power dissipation by more than 66% as shown by HSPICE simulation while driving three branches. The proposed circuits have been fabricated and its effectiveness has been verified by measurement results.

Similar content being viewed by others

References

Liu D, Svensson C. Power consumption estimation in CMOS VLSI chips. IEEE J Solid-State Circ, 1994, 29: 663–670

Qiao F, Yang H Z, Huang G, et al. Implementation of low-swing differential interface circuits for high-speed on-chip asynchronous interconnection. Sci China Ser F-Inf Sci, 2008, 51: 975–984

Zhang H, George V, Rabaey J M. Low-swing on-chip signaling techniques: effectiveness and robustness. IEEE Trans VLSI Syst, 2000, 8: 264–272

Pangjun J, Sapatnekar S S. Low-power clock distribution using multiple voltages and reduced swings. IEEE Trans VLSI Syst, 2002, 10: 309–318

Rjoub A, Koufopavlou O. Low voltage swing gates for low power consumption. In: Proc IEEE Int Symp Circ Syst, Orlando, USA, 1999. 1: 234–237

Asgari F H A, Sachdev M. A low-power reduced swing global clocking methodology. IEEE Trans VLSI Syst, 2004, 12: 538–545

Larsson P. Parasitic resistance in an MOS transistor used as on-chip decoupling capacitance. IEEE J Solid-State Circ, 1997, 32: 574–576

Wang C Y. Implementation of space-efficient voltage-insensitive capacitances in integrated circuits. In: IEEE International Symposium on Circuits and Systems, Island of Kos, Greece, 2006. 1876–1879

Chang Y W, Chang H W, Lu T C, et al. Charge-based capacitance measurement for bias-dependent capacitance. IEEE Electr Device Lett, 2006, 27: 390–392

Rabaey J M, Chandrakasan A, Nikolic B. Digital Integrated Circuits: A Design Perspective. 2nd ed. Beijing: Publishing House of Tsinghua University, 2004. 18–22, 138–144, 188

Rjoub A, Koufopavlou O. Efficient drivers, receivers and repeaters for low power CMOS bus architectures. In: Proc IEEE International Conference on Electronics, Circuits and Systems, Pafos, Cyprus, 1999, 2: 789–794

Svensson C. Optimum voltage swing on on-chip and off-chip interconnect. IEEE J Solid-State Circ, 2001, 36: 1108–1112

Liu Y, Cai J P, Hao Y, et al. A low swing differential signaling circuit for on-chip global interconnects. In: Proc. International Conference on Solid-State and Integrated-Circuit Technology. Beijing, China, 2008. 1693–1696

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wu, F., Jia, S., Wang, Y. et al. Low swing drivers based on charge redistribution. Sci. China Inf. Sci. 53, 2377–2388 (2010). https://doi.org/10.1007/s11432-010-4084-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-010-4084-8