Abstract

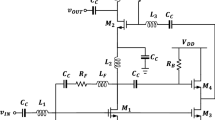

Electrostatic discharge (ESD) failure has become an emerging challenge for radio frequency (RF) integrated circuits (ICs), which requires high ESD-protection for circuit applications in harsh environment. This paper discusses the design and optimization of an ultra-wideband (UWB) correlator circuit using ESDaware simulation design technique. Mixed-mode ESD simulation-design method and RF ESD characterization technique are presented for accurate ESD device design and ESD-induced parasitic effects extraction. The impact of ESD induced parasitic is carefully considered in the whole correlator design simulation by using a direct S-parameter insertion technique. The design is based on a commercial 0.18 μm RFCMOS technology.

Similar content being viewed by others

References

Federal Communications Commission. Report & Order: Revision of Part 15 of the Commission’s Rules Regarding UWB Transmission System. 1st ET Docket 98-153, 2002

Medi A, Namgoong M. A high data-rate energy-efficient interference-tolerant fully integrated CMOS frequency channelized UWB transceiver for impulse radio. IEEE J Solid-State Circ, 2008, 43: 974–980

Hu J, Zhu Y, Wang S, et al. Energy efficient, reconfigurable, distributed pulse generation and detection in UWB impulse radios. In: IEEE Int Ultra-Wideband Conference, 2009. 773–777

Kulkarni V, Muqsith M, Niitsu K, et al. A 750 Mb/s, 12pJ/b, 6–10 GHz CMOS IR-UWB transmitter with enbedded on-chip antenna. IEEE J Solid-State Circ, 2009, 44: 393–403

ESDA/JEDEC Joint Standard. For Electrostatic Discharge Sensitivity Testing—Human Body Model (HBM)—Component Level, ANSI/ESD STM5. 1-2007, Nov. 2007

Chae M, Yang Z, Yuce M, et al. A 128-channel 6 mW wireless neural recording IC with spike feature extraction and UWB transmitter. IEEE Trans Neural Syst Rehabil Eng, 2009, 17: 312–321

Kim C, Nooshabadi S. Design of a tunable all-digital UWB pulse generator CMOS chip for wireless endoscope. IEEE Trans Biomed Circ Syst, 2010, 4: 118–124

Lin L, Wang X, Wang A, et al. Whole-chip ESD protection design verification by CAD. In: EOS/ESD Symposium, Anaheim, CA, 2009. 28–37

Wang A, Zhan R, Feng H, et al. A review on RF ESD protection design. IEEE Electron Dev, 2005, 52: 1304–1311

Xie H, Zhan R Y, Wang A, et al. A pulse-based full-band UWB transceiver SoC in 0.18 μm SiGe BiCMOS. In: IEEE International SoC Conference, 2006. 73–76

Feng H, Chen G, Wang A, et al. A mixed-mode ESD protection circuit simulation-design methodology. IEEE J Solid-State Circ, 2003, 38: 995–1006

Xie H, Chen G, Wang A, et al. A broadband CMOS multiplier-based correlator for IR-UWB transceiver SoC. In: IEEE RFIC Symposium, 2007. 493–496

Qin B, Wang X, Wang A, et al. A single chip 33pJ/pulse 5th-derivative Gaussian based IR-UWB transmitter in 0.13 μm CMOS. In: IEEE Symposium on Circuits and Systems (ISCAS), 2009. 401–404

Guan X, Wang X, Wang A, et al. ESD-RFIC co-design methodology. In: IEEE RFIC Symposium, 2008. 467–470

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Shi, Z., Wang, A. & Cheng, Y. An optimized UWB correlator design with the consideration of the impacts from the ESD protection devices. Sci. China Inf. Sci. 56, 1–9 (2013). https://doi.org/10.1007/s11432-012-4665-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-012-4665-9