Abstract

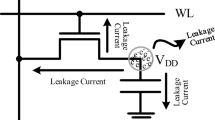

Dynamic random access memory (DRAM) is facing the challenge of technology scaling. The decreasing feature size makes it harder to make DRAM cells which can keep the current data-holding time. When DRAM cells cannot hold data for a long time, DRAM chips need a more frequent refreshing operation. Therefore, in the near future, time and energy cost on DRAM refreshing will be no longer trivial. In this paper, we propose DRAM Error Correction Pointer (ECP), an error-correction-manner framework, to reduce DRAM refreshes without data loss. We exploit the non-uniform feature of DRAM cells with respect to the data retention time. Compared with the conventional refreshing mechanisms, which refresh DRAM chips by the retention time of the leakiest cells, we refresh the chips much fewer times, and treat the not-in-time refreshed cells as fault elements. We use the structure of ECP as a fault tolerant element. By recording the data which are supposed to be written into the leaky cells in our DRAM-ECP structures, DRAM-ECP can significantly decrease refreshing frequency. When these data are to be read out, DRAM-ECP retrieves the data stored in ECPs and covers them to the corresponding position in the data row. Our experiments show that DRAM-ECP can reduce over 70% refreshing operations than the current refreshing mechanism and also get significant energy saving.

摘要

创新点

随着半导体工艺特征尺寸的降低, 在增加 DRAM 存储密度的同时维持原有的数据存储时间越来越困难. 而 DRAM 存储单元数据保持时间的缩短使得 DRAM 的刷新变得更加频繁, 由此带来的能耗和时间代价将不可忽视. 我们提出了 DRAM-ECP, 使用纠错思想的技术降低 DRAM 的刷新频率. 我们充分利用了存储单元数据保持时间的差异特征, 将极少数数据保持时间较短的单元视为故障单元, 将这些单元的数据保存在访存控制器上额外的存储结构中. 这种技术可以大大延长 DRAM 整体刷新周期, 减少超过 70%的 DRAM 的刷新操作, 并可以带来显著的能耗节约.

Similar content being viewed by others

References

Yoon JH, Hunter HC, Tressler GA. Flash & DRAM Si scaling challenges, emerging non-volatile memory technology enablement. In: Flash Memory Summit, 2013

Cha SY. DRAM and future commodity memories. VLSI Technology Short Course, 2011

Kim K, Lee J. A new investigation of data retention time in truly nanoscaled DRAMs. IEEE Electron Dev Lett, 2009, 30: 846–848

Kim Y, Daly R, Kim J, et al. Flipping bits in memory without accessing them: an experimental study of DRAM disturbance errors. In: Proceedings of the 41st International Symposium on Computer Architecture (ISCA), Minneapolis, 2014. 361–372

Hellebrand S, Wunderlich H, Ivaniuk A, et al. Error detecting refreshment for embedded DRAMs. In: Proceedings of the 17th IEEE VLSI Test Symposium, Dana Point, 1999. 384–390

Kim J, Papaefthymiou M. Block-based multiperiod dynamic memory design for low data-retention power. IEEE Trans Very Large Scale Integr Syst, 2003, 11: 1006–1018

Kim J, Papaefthymiou M. Block-based multi-period refresh for energy efficient dynamic memory. In: Proceedings of the 14th ASIC/SOC Conference, Arlington, 2001. 193–197

Ohsawa T, Kai K, Murakami K. Optimizing the DRAM refreshing count for merged DRAM/logic LSIs. In: Proceedings of International Symposium on Low Power Electronics and Design, Monterey, 1998. 82–87

Katayama Y, Stuckey EJ, Morioka S, et al. Fault-tolerant refreshing power reduction of drams for quasi-nonvolatile data retention. In: Proceedings of IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Albuquerque, 1999. 311–318

Ghosh M, Lee HS. Smart refreshing: an enhanced memory controller design for reducing energy in conventional and 3d die-stacked drams. In: Proceedings of the 40th International Symposium on Microarchitecture, Chicago, 2007. 134–145

Emma PG, Reohr WR, Meterelliyoz M. Rethinking refreshing: increasing availability and reducing power in DRAM for cache applications. IEEE Micro, 2008, 28: 47–56

Wilkerson C, Alameldeen AR, Chishti Z, et al. Reducing cache power with low-cost, multi-bit error correcting codes. ACM SIGARCH Comput Architect News, 2010, 03: 83–93

Venkatesan R, Herr S, Rotenberg E. Retention-aware placement in dram (rapid): software methods forquasi-nonvolatiledram. In: Proceedings of International Symposium on High Performance Computer Architecture, Austin, 2006. 155–165

Liu J, Jaiyen B, Veras R, et al. RAIDR: retention-aware intelligent DRAM refresh. In: Proceedings of the 39th Annual International Symposium on Computer Architecture (ISCA), Portland, 2012. 1–12

Isen C, John L. ESKIMO: energy savings using semantic knowledge of inconsequential memory occupancy for DRAM subsystem. In: Proceedings of the 42nd IEEE/ACM International Symposium on Microarchitecture, New York, 2009. 337–346

Liu S, Pattabiraman K, Moscibroda T, et al. Flikker: saving DRAM Refresh-power through critical data partitioning. ACM SIGPLAN Notices, 2012, 39: 213–224

Hamming RW. Error detecting and error correcting codes. Bell Syst Tech J, 1950, 29: 147–160

Mcnairy C, Bhatia R. Montecito: a dual-core, dual-thread Itanium processor. IEEE Micro, 2005, 25: 10–20

Schechter S, Loh GH, Strauss K, et al. Use ECP, not ECC, for hard failures in resistive memories. In: Proceedings of the 37th International Symposium on Computer Architecture (ISCA), Saint-Malo, 2010. 141–152

Bonomi F, Mitzenmacher M, Panigrahy R, et al. An improved construction for counting bloom filters. In: Proceedings of the 14th Annual European Symposium on Algorithms, Zurich, 2006. 684–695

Panneton F, L’Ecuyer P. On the xorshift random number generators. ACM Trans Model Comput Simul, 2005, 15: 346–361

Beckmann B, Binkert N, Black G, et al. The gem5 simulator. Comput Architect News, 2011, 39: 1–7

Rosenfeld P, Cooper-Balis E, Jacob B. DRAMSim2: a cycle accurate memory system simulator. Comput Architect Lett, 2011, 10: 16–19

Singh JP, Weber WD, Gupta A. SPLASH-2: stanford parallel applications for shared-memory. Comput Architect News, 1995, 20: 5–44

Ahmadi M, Wong S. A cache architecture for counting bloom filters. In: Proceedings of the 15th IEEE International Conference on Networks, Adelaide, 2007. 218–223

Kim C, Kong B, Lee C, et al. CMOS temperature sensor with ring oscillator for mobile DRAM self-refresh control. Microelectron J, 2007, 38: 1042–1049

Emma PG, Reohr WR, Wang L. Restore tracking system for DRAM.U.S. patent No 6389505, 2002

Pawlowski JT. Intelligent refreshing controller for dynamic memory devices. U.S patent No 5890198, 1999

Song SP. Method and system for selective DRAM refreshing to reduce power consumption. U.S. patent No 6094705, 2000

Nair PJ, Kim DH, Qureshi MK, et al. ArchShield: architectural framework for assisting dram scaling by tolerating high error rates. In: Proceedings of the 40th International Symposium on Computer Architecture (ISCA), Tel-Aviv, 2013. 72–83

Seong NH, Woo DH, Srinivasan V, et al. SAFER: stuck-at-fault error recovery for memories. In: Proceedings of the 43rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), Atlanta, 2010. 115–124

Stuecheli J, Kaseridis D, Hunter HC, et al. Elastic refresh: techniques to mitigate refresh penalties in high density memory. In: Proceedings of the 43rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), Atlanta, 2010. 375–384

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Zhu, D., Wang, R., Wei, Y. et al. Reducing DRAM refreshing in an error correction manner. Sci. China Inf. Sci. 58, 1–14 (2015). https://doi.org/10.1007/s11432-015-5352-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-015-5352-4