Abstract

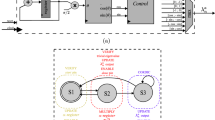

In this paper, an efficient architecture for the Finite Ridgelet Transform (FRIT) suitable for VLSI implementation based on a parallel, systolic Finite Radon Transform (FRAT) and a Haar Discrete Wavelet Transform (DWT) sub-block, respectively is presented. The FRAT sub-block is a novel parametrisable, scalable and high performance core with a time complexity of O(p 2), where p is the block size. Field Programmable Gate Array (FPGA) and Application Specific Integrated Circuit (ASIC) implementations are carried out to analyse the performance of the FRIT core developed.

Similar content being viewed by others

References

Do, M.N., Vetterli, M.: Orthonormal finite ridgelet transform for image compression. In: Proceedings of the 2000 International Conference on Image Processing, vol. 2, pp. 367–370, September (2000)

Do, M.N., Vetterli, M.: Contourlets: a directional multiresolution image representation. In: Proceedings of 2002 International Conference on Image Processing, vol. 1, pp. I–357 to I–360, September (2002)

Candes, E.J., Donoho, D.L.: A surprisingly effective nonadaptive representation for objects with edges. Curves and surfaces, pp. 105–120. Vanderbilt University Press, Nashville (2000)

Matus, F., Flusser, H.: Image representation via a finite radon transform. IEEE. Trans. Pattern. Anal. Mach. Intell. 15, 996–1006 (1993)

“Handel-C Language Reference," Celoxica Ltd

Candes, E.J.: Ridgelets: theory and application. Dissertation, Dept. of Stats, Stanford University (1998)

Bolker, E.D.: “The Finite Radon Transform.” Contemp. Math. 63, 27–50 (1987)

Wisinger, J., Mahapatra, R.: FPGA based image processing with the curvelet transform. Texas A and M University, TX, Technical Report TR-CS-2003-01-0 (2003)

Uzun, I.S., Amira, A.: Design and FPGA implementation of finite ridgelet transform. IEEE Int Symp Circuits Syst 6, 5826–5829 (2005)

Rahman, C.A., Badawy, W.: Architectures the finite radon transform. IEE Electron Lett 40, 931–932 (2004)

Chandrasekaran, S., Amira, A.: High speed/low power architectures for the finite radon transform. International Conference on Field Programmable Logic and Applications 6, 5826–5829 (2005)

DK Design Suit (2004) Version 1.1 ed., Celoxica Ltd

RC1000 data sheet, Celoxica Ltd

Virtex-E 1.8 V Field Programmable Gate Arrays, Xilinx Inc., Datasheet DS022-1 (v2.3), July 2002

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chandrasekaran, S., Amira, A., Minghua, S. et al. An efficient VLSI architecture and FPGA implementation of the Finite Ridgelet Transform. J Real-Time Image Proc 3, 183–193 (2008). https://doi.org/10.1007/s11554-008-0081-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11554-008-0081-1