Abstract

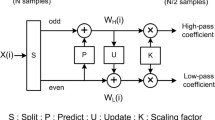

In the literature, techniques such as pipelining and wave-pipelining (WP) are proposed for increasing the operating frequency of a digital circuit. In general, use of pipelining results in higher speed at the cost of increase in the area and clock routing complexity. On the other hand, use of WP results in less clock routing complexity and less area but enables the digital circuit to be operated only at moderate speeds. In this paper, a hybrid wave-pipelining scheme is proposed to get the benefits of both pipelining and WP techniques. Major contributions of this paper are: proposal for the implementation of 2D DWT using lifting scheme by adopting the hybrid wave-pipelining and proposal for the automation of the choice of clock frequency and clock skew between the input and output registers of wave-pipelined circuit using built in self test (BIST) and system-on-chip (SOC) approaches. In the hybrid scheme, different lifting blocks are interconnected using pipelining registers and the individual blocks are implemented using WP. For the purpose of evaluating the superiority of the schemes proposed in this paper, the system for the computation of one level 2D DWT is implemented using the following techniques: pipelining, non-pipelining and hybrid wave-pipelining. The BIST approach is used for the implementation on Xilinx Spartan-II device. The SOC approach is adopted for implementation on Altera and Xilinx field programmable gate arrays (FPGAs) based SOC kits with Nios II or Micro blaze soft-core processors. From the implementation results, it is verified that the hybrid WP circuit is faster than non-pipelined circuit by a factor of 1.25–1.39. The pipelined circuit is in turn faster than the hybrid wave-pipelined circuit by a factor of 1.15–1.38 and this is achieved with the increase in the number of registers by a factor of 1.79–3.15 and increase in the number of LEs by a factor of 1.11–1.65. The soft-core processor based automation scheme has considerably reduced the effort required for the design and testing of the hybrid wave-pipelined circuit. The techniques proposed in this paper, are also applicable for ASICs. The optimization schemes proposed in this paper are also applicable for the computation of other image transforms such as DCT, DHT.

Similar content being viewed by others

References

Xilinx documentation library, Xilinx Corporation, USA

Altera documentation library-2003 Altera Corporation, USA

Sheldon, D., Kumar, R., Vahid, F., Tullsen, D., Lysecky, R.: Conjoining soft-core FPGA processors. In: IEEE/ACM International Conference on Computer Aided Design, 2006, ICCAD, pp. 694–701 (2006)

Draper, B.A., Beveridge, J.R., Willem Bohm, A.P., Ross, C., Chawathe, M.: Accelerated image processing on FPGAs. IEEE Trans. Image. Process. 12(12), 1543–1551 (2003)

Ritter, J., Molitor, P.: A pipelined architecture for partitioned DWT based lossy image compression using FPGA’s. In: Proceedings ACM Conference FPGA 2001, pp. 201–206 (2001)

Lakshminarayanan, G., Venkataramani, B., Senthil Kumar, J., Yousuf, A.K., Sriram, G.: Design and FPGA implementation of image block encoders with 2D-DWT. Proceedings TENCON 2003. 3, 1015–1019 (2003)

Daubechies, I., Sweldens, W.: Factoring wavelet transforms into lifting steps. J. Fourier Anal. Appl. 4, 247–269 (1998)

Nyathi, J., Delgado-Frias, J.G.: A hybrid wave-pipelined network router. IEEE Trans. Circuits. Syst-I, Fundam. Theory. Appl. 49(12), 1764–1772 (2002)

Hauck, O., Katoch, A., Huss, S.A.: VLSI system design using asynchronous wave pipelines: a 0.35 μm CMOS 1.5 GHz elliptic curve public key cryptosystem chip. In: Proceeding of sixth international symposium on advanced research in asynchronous circuits and systems 2000 (ASYNC 2000), pp. 188–197 (2000)

Burleson, W.P., Ciesielski, M., Klass, F., Liu, W.: Wave-pipelining: a tutorial and research survey. IEEE Trans. Very Large Scale Integration (VLSI) Syst. 6(3), 464–474 (1998)

Gray, T.C., Liu, W., Cavin, R.K., III.: Wave-Pipelining: Theory and CMOS Implementation. Kluwer, Boston (1994)

Parhi, K.K.: VLSI Signal Processing Systems. Wiley, New York (1999)

Boemo, E.I., Lopez-Buedo, S., Meneses, J.M.: Wave-pipelines via look-up tables. IEEE Int. Symp. Circuits Syst. (ISCAS ’1996). 4, 85–88 (1996)

Lakshminarayanan, G., Venkataramani, B.: Optimization techniques for FPGA based wave-pipelined DSP blocks. IEEE Trans. Very Large Scale Integration (VLSI) Syst. 13(7), 783–793 (2005)

Aharya, T., Tsai, P.-S.: JPEG2000 Standard for Image Compression Concepts Algorithms and VLSI Architectures. Wiley, New York (2005)

Sayood, K.: Introduction to Data Compression. Morgan Kaufmann, Menlo Park (2000). An Imprint of Elsevier

Smith, M.J.S.: Application Specific Integrated Circuits. Pearson Education Asia Pvt. Ltd, Singapore (2003)

Seetharaman, G., Venkataramani, B., Lakshminarayanan, G.: Design and FPGA implementation of self tuned wave-pipelined filters. IETE J. Res. 524, 281–286 (2006)

Seetharaman, G., Venkataramani, B., Lakshminarayanan, G.: Design and FPGA implementation of wave-pipelined image block encoders using 2D-DWT. In: Proceedings of VLSI design and test symposium VDAT 2005, pp. 12–20 (2005)

Seetharaman, G., Venkataramani, B., Lakshminarayanan, G.: Design and FPGA implementation of wave-pipelined distributed arithmetic based filters. In: Proceedings of VLSI Design and Test workshop VDAT 2004, pp. 216–220 (2004)

Amudha, V., Venkataramani, B., Vinoth Kumar, R., Ravishankar, S.: SOC Implementation of HMM Based Speaker Independent Isolated Digit Recognition System. In: 20th International IEEE Conference on VLSI Design (VLSID’07), pp. 1–6 (2007)

Seetharaman, G., Venkataramani, B., Amudha, V., Saundattikar, A.: System on chip implementation of 2D DWT using lifting scheme. In: Proceedings of the International Asia and South Pacific Conference on Embedded SOCs (ASPICES 2005), (2005)

Seetharaman, G., Venkataramani, B.: SOC implementation of wave-pipelined circuits. Proceedings of IEEE International conference on Field Programmable Technology 2007 (ICFPT 2007), pp. 9–16 (2007)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Seetharaman, G., Venkataramani, B. & Lakshminarayanan, G. Automation techniques for implementation of hybrid wave-pipelined 2D DWT. J Real-Time Image Proc 3, 217–229 (2008). https://doi.org/10.1007/s11554-008-0087-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11554-008-0087-8