Abstract

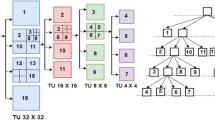

This paper presents fast and low-complexity architecture to implement the computation of 16 × 16 luminance and 8 × 8 chrominance blocks for H.264 intra prediction. To conserve arithmetic operators and hasten processing speed, we propose an architecture based on recycled computation without the need for a multiplier. Center-based computation is used to generate the pixels in plane mode using two parallel cores and the architecture is implemented using four-parallel inputs and two-parallel outputs to achieve high-speed processing. The architecture is a configurable structure capable of computing the parameters and generating the predicted pixels in DC and plane mode within only 239 cycles in the processing of YUV blocks. The high-speed prediction for H.264 encoding meets the requirement for real-time HDTV.

Similar content being viewed by others

References

ITU-TRec.H.264/ISO/IEC14496-10AVC in Joint Video Team (JVT) of ISO/IECMPE Gand ITU-TVCEG, JVT G050, (2003)

Parlak, M., Adibelli, Y., Hamzaoglu, I.: A novel computational complexity and power reduction technique for H.264 intra prediction. IEEE Trans Consumer Electron. 54(4), 2006–2014 (2008)

Hsia, S.-C., Chou, Y.-C.: Fast intra-prediction with near pixel correlation approach for H.264/AVC System. IET (IEE) Image Process 2(4 ), 185–193 (2008)

Sahin, E., Hamzaoglu, I.: An efficient hardware architecture for H.264 intra prediction algorithm. Design, automation and test in Europe Conference, April (2007)

Lin, H.Y., Wu, K.H., Liu, B.D., Yang, J.F.: An efficient VLSI architecture for transform-based intra prediction in H.264/AVC. IEEE Trans. Circuit Syst. Video Technol. 20(6), 894–906 (2010)

Wang, J.C., Wang, J.F., Yang, J.F., Chen, J.T.: A fast mode decision algorithm and its VLSI design for H.264/AVC intra-prediction. IEEE Trans. Circuits Syst. Video Technol. 17(10), 1414–1422 (2007)

Xu, K., Choy, C.S.: A power-efficient and self-adaptive prediction engine for H.264/AVC decoding. IEEE Trans. VLSI Syst. 16(3), 302–313 (2008)

Palnitkar, S.: Veriolg HDL. Prentice Hall, Nj07458 (1996)

Xilinx Corp. Web., http://www.xilinx.com. Accessed 2 March 2012

Acknowledgments

This work was supported by the National Science Council, Taiwan, under nsc 96-2221-E-327-006-MY3-3.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Hsia, SC., Hsu, WC. & Chou, YC. Fast low-complexity computation and real-time architecture for H.264/AVC intra-prediction. J Real-Time Image Proc 9, 589–595 (2014). https://doi.org/10.1007/s11554-012-0245-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11554-012-0245-x