Abstract

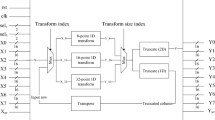

The paper presents a cost-shared architecture to compute multiple integer discrete cosine transform (Int-DCT) of four video codecs—AVS, H.264/AVC, VC-1 and HEVC (under development). Based on the symmetric structure of the matrices and the similarity in matrix operation, we develop a generalized “decompose and share” algorithm to compute both 4 × 4 and 8 × 8 Int-DCT. The algorithm is later applied to the video codecs. The hardware share approach ensures maximum circuit reuse during the computation. The architecture is designed with only adders and shifters to reduce the hardware cost significantly. The design is implemented on FPGA and later synthesized in CMOS 0.18 μm technology.

Similar content being viewed by others

References

Standard for Television: VC-1 Compressed Video Bitstream Format and Decoding Process, SMPTE 421M (2006)

ITU-T Rec. H.264/ISO/IEC 14496-10 AVC, 2003

GB/T 20090.1 Information technology: Advanced coding of audio and video—Part 1: System, Chinese AVS standard

Sullivan, G.J., Ohm, J.-R.: Recent developments in standardization of high efficiency video coding (HEVC). In: SPIE Applications of Digital Image Processing XXXIII, vol. 7798, Aug 2010

Chi-Cheng, J., et al.: A Full-HD 60 fps AVS/H.264/VC-1/MPEG-2 video decoder for digital home applications. In: Proceedings of International Symposium on VLSI-DAT, pp. 1–4, April 2011

Vetro, A., Christopoulos, C., Huifang, S., Mitsubishi, E.R.L., Hill, M.: Video transcoding architectures and techniques: an overview. IEEE Signal Process. Magz. 20, 18–29 (2003)

Gao, W., et al.: AVS video coding standard. Intel. Multimedia Commun Tech. Appli. SCI 280, 125–166 (2010)

Wiegand, T., Sullivan, G., Bjøntegaard, G., Luthra, A.: Overview of the H.264/AVCvideo coding standard. IEEE Trans. Circuits Syst. Video Technol. 13(7), 560–576 (2003)

Joint Collaborative Team: Video Coding: CE10: Core transform design for HEVC. JCTVC-G495, Geneva, Switzerland, 21–30 Nov, 2011

Lee, S., Cho, K.: Architecture of transform circuit for video decoder supporting multiple standards. Electron Lett 44(4), 274–275 (2008)

Kim, S., Chang, H., Lee, S., Cho, K.: VLSI design to unify IDCT and IQ circuit for multistandard video decoder. In: Proceedings of ISIC International Symposium Prototyping, pp. 328–331, 2008

Qi, H., Huang, Q., Gao, W.: A low-cost very large scale integration architecture for multistandard inverse transform. IEEE Trans. Circuits Syst. II 57(7), 551–555 (2010)

Lee, S., Cho, K.: Circuit implementation for transform and quantization operations of H.264/MPEG-4/VC-1 video decoder. In: Proceedings of International Conference of Design and Technology of Integrated Systems in Nanoscale Era, pp. 102–107, Sept 2007

Wahid, K., Martuza, M., Das, M., McCrosky, C.: Efficient hardware implementation of 8 × 8 integer cosine transforms for multiple video codecs. J. Real-Time Image Process. (2011). doi:10.1007/s11554-011-0209-6

Liu, G.: An area-efficient IDCT architecture for multiple video standards. In: Proceedings of 2nd International Conference ICISE, pp. 3518–3522, Dec 2010

Fan, C.P., Su, G.A.: Efficient low-cost sharing design of fast 1-D inverse integer transform algorithms for H.264/AVC and VC-1. IEEE Signal Process. Lett. 15, 926–9292 (2010)

Fan, C., Su, G.: Fast algorithm and low-cost hardware-sharing design of multiple integer transforms for VC-1. IEEE Trans. Circuits Syst. II 56, 788–792 (2009)

Zhou, Dajiang, et al.: A 1080p@60fps multi-standard video decoder chip designed for power and cost efficiency in a system perspective. Symp. VLSI Circuits 2009, 262–263 (2009)

Fan, C.P., Lin, Y.L.: Implementations of low cost hardware sharing architectures for Fast 8 × 8 and 4 × 4 Integer Transforms in H.264/AVC. IEICE Trans. Fund. Elect. Commun. Compt. 90, 511–516 (2007)

Chao, Y.C., et al.: An efficient architecture of multiple 8 × 8 Transforms for H.264/AVC and VC-l decoders. In: Proceedings of International Conference on Green Circuits and Systems, pp. 595–598, 2010

Wang, K., et al.: A Reconfigurable Multi-Transform VLSI Architecture Supporting Video Codec Design. IEEE Trans. Circuits Syst. II Exp Briefs 58(7), 432–436 (2011)

Fan, C.P., et al.: Fast Multiple Inverse Transforms with Low-Cost Hardware Sharing Design for Multistandard Video Decoding. IEEE Trans. Circuits Syst. II Exp. Briefs 58(8), 517–521 (2011)

Li, Y., He, Y., Mei, S.L.: A highly parallel joint VLSI architecture for transforms in H.264/AVC. J. Signal Process. Syst. 50(1), 19–32 (2008)

Su, G.A., Fan, C.P.: Low-cost hardware-sharing architecture of fast 1-D inverse tranforms for H.264/AVC and AVS applications. IEEE Trans. Circuits Syst. II, Exp Briefs 45(12), 1249–12153 (2008)

Acknowledgments

The authors would like to acknowledge the Natural Science and Engineering Research Council of Canada (NSERC) for its support to this research work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Martuza, M., Wahid, K.A. Implementation of a cost-shared transform architecture for multiple video codecs. J Real-Time Image Proc 10, 151–162 (2015). https://doi.org/10.1007/s11554-012-0266-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11554-012-0266-5