Abstract

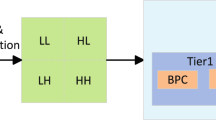

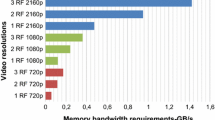

To detect fast myoclonus jerks, doctors require a full-HD video capture of the patient at 100 frames per second. Real-time video compression becomes mandatory to archive/transmit the generated data. To achieve this goal, we used a certified medical imaging coder based on discrete wavelet transform (DWT). Thus, a major challenge was to design a 2D DWT architecture, achieving the throughput of 100 full-HD frames/s. The novel unified 2D DWT computation architecture performs both horizontal and vertical transform simultaneously and eliminates the problem of column-wise image pixel accesses to/from the off-chip DDR RAM. All of these factors have led to the reduction of the required off-chip DDR RAM bandwidth by more than 2X. The proposed concept uses four-port line buffers leading to pipelined parallel processing of direct memory access (DMA) read, horizontal 1D DWT, vertical 1D DWT, and DMA write. The proposed architecture has cycles per pixel of just 1/8, making it far exceeds 100 full-HD fps and well positioned for the 4K and 8K video processing. Finally, we highlighted that the developed architecture is highly scalable, outperforms state of the art and is deployed in a first video EEG medical prototype.

Similar content being viewed by others

References

Lambert, L., Despatin, J., Dhif, I., Mhedhbi, I., Ibraheem, M.S., Syed-Zahid, A., Granado, B., Hachicha, K., Pinna, A., Garda, P., Kaddouh, F., Terosiet, M., Histace, A., Romain, O., Bellet, C., Durand, F., Commes, J.P., Hochberg, S., Heudes, D., Lozeron, P., Kubis, N.: Telemedecine, electroencephalography and current issues. SMART-EEG: an innovative solution. Eur. Res. Telemed. 4(3), 81–86 (2015)

Taubman, D.S., Michael, W.M., Rabbani, M.: JPEG 2000: image compression fundamentals, standards and practice. J. Electron. Imaging 11(2), 286–287 (2002)

Mhedhbi, I., Kaddouh, F., Hachicha, K., Heudes, D., Hochberg, S., Garda, P.: Mask motion adaptive medical image coding. In: IEEE-EMBS International Conference on Biomedical and Health Informatics (BHI), pp. 408–411 (2014)

Ysitcom.: Waaves compression format (2017) http://en.ysitcom.com/

Philippe, H.S.: Procede de decodage d’image et dispositif de mise en oeuvre de ce procede. WO Patent App. PCT/FR2004/001,942 (2005)

Öktem, L., Astola, J.: Hierarchical enumerative coding of locally stationary binary data. Electron. Lett. 35(17), 1428–1429 (1999)

Lambert, L., Hachicha, K., Ahmed, S.Z., Pinna, A., Garda, P.: Synchronizing physiological data and video in a telemedicine application: a multimedia approach. In: 2015 37th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), pp. 181–185 (2015)

Mallat, S.G.: A theory for multiresolution signal decomposition: the wavelet representation. IEEE Trans. Pattern Anal. Mach. Intell. 11(7), 674–693 (1989)

Daubechies, I., Sweldens, W.: Factoring wavelet transforms into lifting steps. J. Fourier Anal. Appl. 4(3), 247–269 (1998)

Xiong, C., Tian, J., Liu, J.: Efficient architectures for two-dimensional discrete wavelet transform using lifting scheme. IEEE Trans. Image Process. 16(3), 607–614 (2007)

Xiong, C.-Y., Tian, J.-W., Liu, J.: Efficient high-speed/low-power line-based architecture for two-dimensional discrete wavelet transform using lifting scheme. IEEE Trans. Circuits Syst. Video Technol. 16(2), 309–316 (2006)

Mohanty, B.K., Meher, P.K.: Memory-efficient high-speed convolution-based generic structure for multilevel 2-D DWT. IEEE Trans. Circuits Syst. Video Technol. 23(2), 353–363 (2013)

Hu, Y., Jong, C.C.: A memory-efficient high-throughput architecture for lifting-based multi-level 2-D DWT. IEEE Trans. Signal Process. 61(20), 4975–4987 (2013)

Andra, K., Chakrabarti, C., Acharya, T.: A VLSI architecture for lifting-based forward and inverse wavelet transform. IEEE Trans. Signal Process. 50(4), 966–977 (2002)

Wu, B.-F., Lin, C.-F.: A high-performance and memory-efficient pipeline architecture for the 5/3 and 9/7 discrete wavelet transform of JPEG2000 codec. IEEE Trans. Circuits Syst. Video Technol. 15(12), 1615–1628 (2005)

Mohanty, B.K., Meher, P.K.: Memory efficient modular VLSI architecture for highthroughput and low-latency implementation of multilevel lifting 2-D DWT. IEEE Trans. Signal Process. 59(5), 2072–2084 (2011)

Aziz, S.M., Pham, D.M.: Efficient parallel architecture for multi-level forward discrete wavelet transform processors. Comput. Electr. Eng. 38(5), 1325–1335 (2012)

Darji, A., Agrawal, S., Oza, A., Sinha, V., Verma, A., Merchant, S.N., Chandorkar, A.N.: Dual-scan parallel flipping architecture for a lifting-based 2-D discrete wavelet transform. IEEE Trans. Circuits Syst. II Express Briefs 61(6), 433–437 (2014)

Sweldens, W.: The lifting scheme: a construction of second generation wavelets. SIAM J. Math. Anal. 29(2), 511–546 (1998)

Liao, H., Mandal, M.K., Cockburn, B.F.: Efficient architectures for 1-D and 2-D lifting-based wavelet transforms. IEEE Trans. Signal Process. 52(5), 1315–1326 (2004)

Darji, A.D., Kushwah, S.S., Merchant, S.N., Chandorkar, A.N.: High-performance hardware architectures for multi-level lifting-based discrete wavelet transform. EURASIP J. Image Video Process. 1, 1–19 (2014)

Sameen, I., Chang, Y.C., Ng, M.S., Goi, B.-M., Ooi, C.-P.: A unified FPGA-based system architecture for 2-D discrete wavelet transform. J. Signal Process. Syst. 71(2), 123–142 (2013)

Hu, Y., Jong, C.C.: A memory-efficient scalable architecture for lifting-based discrete wavelet transform. IEEE Trans. Circuits Syst. II Express Briefs 60(8), 502–506 (2013)

Cohen, A., Daubechies, I., Feauveau, J.-C.: Biorthogonal bases of compactly supported wavelets. Commun. Pure Appl. Math. 45(5), 485–560 (1992)

Mathworks.: Matlab (2017) https://www.mathworks.com/

Wang, Z., Bovik, A.C., Sheikh, H.R., Simoncelli, E.P.: Image quality assessment: from error visibility to structural similarity. IEEE Trans. Image Process. 13(4), 600–612 (2004)

Hsia, C.H., Chiang, J.S., Guo, J.M.: Memory-efficient hardware architecture of 2-D dual-mode lifting-based discrete wavelet transform. IEEE Trans. Circuits Syst. Video Technol. 23(4), 671–683 (2013)

Bai, Y., Ahmed, S.Z., Granado, B.: FPGA implementation of hierarchical enumerative coding for locally stationary image source. In: 2013 23rd International Conference on Field programmable Logic and Applications, pp 1–6 (2013)

Acknowledgements

This paper is based upon the work in the Smart EEG project. This project is conducted jointly with the companies CIRA, Partelec, ACACIA, 2CSI, the hospitals Georges Pompidou and Lariboisiere, ETIS and LIP6 labs. The authors thank all the project members for their constructive debate.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ibraheem, M.S., Hachicha, K., Ahmed, S.Z. et al. High-throughput parallel DWT hardware architecture implemented on an FPGA-based platform. J Real-Time Image Proc 16, 2043–2057 (2019). https://doi.org/10.1007/s11554-017-0711-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11554-017-0711-6