Abstract

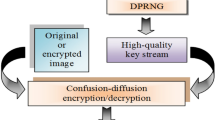

In this paper a new approach for designing invisible non-blind full crypto-watermarking system targeting images security on FPGA platform is presented. This new design is based on the Hardware-Software co-design approach using the High-Level Synthesis (HLS) tool of Xilinx which allows a good compromise between development time and performances. For a better authentication and robustness of the proposed system, the Discrete Wavelet Transform (DWT) is employed. To more enhance the security level, a new chaos-based generator proposed is integrated into a stream cipher algorithm in order to encrypt and decrypt the watermark during the insertion and extraction phases.This approach allows a better secure access at the positions of the watermark and to distribute the watermark evenly throughout the image. Three novel customized Intellectual Property (IP) cores designed under HLS tool, implementing Haar DWT and the new chaos-based key generator, have been generated, tested, and validated. The generated Register Transfer Level-IP (RTL-IP) cores are integrated into a Vivado library that achieves real-time secured watermarking operations for both embedding and extraction processes. The system has been evaluated using the main metrics in terms of imperceptibility of the produced watermarked images achieving a Peak Signal to Noise Ratio (PSNR) of 47 dB, robustness against most geometric and image processing attacks achieving a Normalized Cross-Correlation (NCC) of 0.99. The proposed crypt-watermarking system allows a good solution against brute force attack which produce a huge key-space of \(2^{768}\). Finally, the implementation offers a good efficiency value of 0.19 MHz/LUT in terms of FPGA resource consumption and speed, making the system a reliable choice for real sensitive embedded applications.

Similar content being viewed by others

References

Coleman, R.: Use of visual communication in public journalism. Newsp. Res. J. 21(4), 17 (2000)

Zhang, J., Sun, J., Wang, J., Yue, X.G.: Visual object tracking based on residual network and cascaded correlation filters, J. Ambient Intell. Hum. Comput. 1:1–14 (2020)

Zhang, J., Wu, Y., Feng, W., Wang, J.: Spatially attentive visual tracking using multi-model adaptive response fusion. IEEE Access 7, 83873 (2019)

Zhang, J., Xie, Z., Sun, J., Zou, X., Wang, J.: A cascaded R-CNN with multiscale attention and imbalanced samples for traffic sign detection. IEEE Access 8, 29742 (2020)

Zhang, J., Wang, W., Lu, C., Wang, J., Sangaiah, A.K.: Lightweight deep network for traffic sign classification. Annal. Telecommun. 75(7), 369 (2020)

Nie, T., Zhou, L., Lu, Z.M.: Fingerprinting methods for intellectual property protection using constraints in circuit partitioning. IET Circuits Devices Syst. 10(3), 237 (2016)

Dridi, M., Hajjaji, M.A., Bouallegue, B., Mtibaa, A.: Cryptography of medical images based on a combination between chaotic and neural network. IET Image Process. 10(11), 830 (2016)

Lorenz, E.N.: The mechanics of vacillation. J. Atmos. Sci. 20(5), 448 (1963)

Pecora, L.M., Carroll, T.L.: Synchronization in chaotic systems. Phys. Rev. Lett. 64(8), 821 (1990)

Rajagopalan, S., Amirtharajan, R., Upadhyay, H.N., Rayappan, J.B.B.: Survey and analysis of hardware cryptographic and steganographic systems on FPGA. J. Appl. Sci. 12(3), 201 (2012)

Das, S., Sunaniya, A.K., Maity, R., Maity, N.P.: Parallel hardware implementation of efficient embedding bit rate control based contrast mapping algorithm for reversible invisible watermarking. IEEE Access 8, 69072 (2020)

Hajjaji, M.A., Gafsi, M., Ben Abdelali, A., Mtibaa, A.: FPGA implementation of digital images watermarking system based on discrete Haar wavelet transform. Secur. Commun. Netw. (2019)

Hazra, S., Ghosh, S., De, S., Rahaman, H.: FPGA implementation of semi-fragile reversible watermarking by histogram bin shifting in real time. J. Real Time Image Process. 14(1), 193 (2018)

Mulani, A.O., Mane, P.: Secure and area efficient implementation of digital image watermarking on reconfigurable platform. Int. J. Innov. Technol. Explor. Eng. (IJITEE) 8(2), 1 (2018)

Maity, G.K., Jana, P., Mandal, H., Chiu, T.L.: Power-aware VLSI design of reversible watermarking for access control. Microsyst. Technol. 1, 1–16 (2019)

Vashistha, A., Joshi, A.M.: Fingerprint based biometric watermarking architecture using integer. DCT 1, 2818–2821 (2016)

Arumugham, S., Rajagopalan, S., Rayappan, J.B.B., Amirtharajan, R.: Tamper-resistant secure medical image carrier: an iwt-svd-chaos-fpga combination. Arab. J. Sci. Eng. 44(11), 9561 (2019)

Phadikar, A., Mandal, H., Chiu, T.L.: Parallel hardware implementation of data hiding scheme for quality access control of grayscale image based on FPGA. Multidimens. Syst. Signal Process. 31(1), 73 (2020)

Das, S., Singh, P., Koley, C.: Hardware implementation of adaptive feedback based reversible image watermarking for image processing application. Microsyst. Technol. 1, 1–17 (2018)

Nayak, M.R., Bag, J., Sarkar, S., Sarkar, S.K.: Hardware implementation of a novel water marking algorithm based on phase congruency and singular value decomposition technique. AEU Int. J. Electron. Commun. 71, 1 (2017)

Chen, J., Fan, H., Sun, Y., Ma, H.: Accelerating digital watermarking algorithm based on SOC pp. 24–33 (2016)

Tolba, M.F., Sayed, W.S., Radwan, A.G., Abd-El-Hafiz, S.K., Soliman, A.M.: Hardware speech encryption using a chaotic generator, dynamic shift and bit permutation pp. 100–103 (2018)

Azzaz, M.S., Tanougast, C., Maali, A., Benssalah, M.: An efficient and lightweight multi-scroll chaos-based hardware solution for protecting fingerprint biometric templates. Int. J. Commun. Syst. 1, e4211 (2019)

Wu, Y., Noonan, J.P., Agaian, S., et al.: NPCR and UACI randomness tests for image encryption, cyber journals: multidisciplinary journals in science and technology. J. Sel. Areas Telecommun. (JSAT) 1(2), 31 (2011)

Vaskova, A., López-Ongil, C., San Millán, E., Jiménez-Horas, A., Entrena, L.: Accelerating secure circuit design with hardware implementation of diehard battery of tests of randomness, In: 2011 IEEE 17th international on-line testing symposium (IEEE), pp. 179–181 (2011)

Alvarez, G., Li, S.: Some basic cryptographic requirements for chaos-based cryptosystems. Int. J. Bifurcation Chaos 16(08), 2129 (2006)

Sudha, M., Thanuja, T.: FPGA implementation of DTCWT and PCA based watermarking technique. Int. J. New Innov. Eng. Technol. 10(1), 3 (2019)

Himadri Mandal, G.K.M.T.L.C., Amit Phadikar, FPGA based low power hardware for quality access control of compressed gray scale image. Microsyst. Technol. 1: 1 (2018)

Hazra, S., Ghosh, S., De, S., Rahman, H.: FPGA implementation of semi-fragile reversible watermarking by histogram bin shifting in real time. J. Real Time Image Process. 14(1), 193 (2018)

Ge, H., Sha, J.: FPGA-based low-complexity high-throughput real-time hardware. J. Real Time Image Process. 16(4), 813 (2019)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare having no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kaibou, R., Azzaz, M.S., Benssalah, M. et al. Real-time FPGA implementation of a secure chaos-based digital crypto-watermarking system in the DWT domain using co-design approach. J Real-Time Image Proc 18, 2009–2025 (2021). https://doi.org/10.1007/s11554-021-01073-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11554-021-01073-3