Abstract

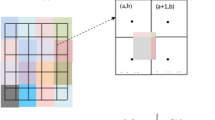

This paper proposes three pipeline VLSI architectures for high-quality image scaling. The proposed architectures use low-complexity v-model spatial sharpening filter, modified edge detection, and simplified bilinear interpolation. Low complexity v-model spatial sharpening filter is obtained by modifying the 3 \(\times\) 3 sharpening kernel to x-model and then to v-model. This sharpening filter enhances the center pixel intensity value relative to the nearest pixels. The modified edge detection technique needs less hardware to find the sharp change in the pixel values. The number of multipliers required for bilinear interpolation is reduced by performing algebraic manipulations. Matlab tool is used analyze the scaled image quality with Peak Signal to Noise Ratio (PSNR) and Structural Similarity (SSIM) parameters. The proposed three VLSI architectures are described using Verilog HDL (hardware description language) and synthesized using Cadence genus compiler using GPDK 90 nm technology. One of the proposed architectures requires 8981 (µm2) area and consumes 1.90 (mW) power, which is less when compared to those of the existing architectures.

Similar content being viewed by others

References

Lee, R., Venieris, S., Dudziak, L., Bhattacharya, S., Lane, N.: Mobisr: efficient on-device super-resolution through heterogeneous mobile processors. In: Proc. MobiCom, pp. 1–16 (2019)

Lee, J., Lee, J., Yoo, H.-Y.: SRNPU: an energy-efficient CNN-based super-resolution processor with tile-based selective super-resolution in mobile devices. IEEE J. Emerg. Sel. Topic Circuits Syst. 10, 320–334 (2020). https://doi.org/10.1109/JETCAS.2020.3014454

Caselles, V., Morel, J.M., Sbert, C.: An axiomatic approach to image interpolation. IEEE Trans. Image Process. 7, 376–386 (1998). https://doi.org/10.1109/83.661188

Meijering, E.H.W., Zuiderveld, K.J., Viergever, M.A.: Image reconstruction by convolution with symmetrical piecewise nth-order polynomial kernels. IEEE Trans. Image Process. 8, 192–201 (1999). https://doi.org/10.1109/83.743854

Jensen, K., Anastassiou, D.: Subpixel edge localization and the interpolation of still images. IEEE Trans. Image Process. 4, 285–295 (1995). https://doi.org/10.1109/83.366477

Keys, R.: Cubic convolution interpolation for digital image processing. IEEE Trans. Acoust. Speech Signal Process. 29, 1153–1160 (1981). https://doi.org/10.1109/TASSP.1981.1163711

Kim, H., Cha, Y., Kim, S.: Curvature interpolation method for image zooming. IEEE Trans. Image Process. 20, 1895–1903 (2011). https://doi.org/10.1109/TIP.2011.2107523

Han, J.W., Kim, J.H., Cheon, S. H., Kim J.O., Ko, S.J.: A novel image interpolation method using the bilateral filter. In: ICCE 2010-2010 Digest of Technical Papers International Conference on Consumer Electronics. pp. 25–26 (2010)

Zhang, X., Wu, X.: Image interpolation by adaptive 2-D auto regressive modeling and soft-decision estimation. IEEE Trans. Image Process. 17, 887–896 (2008). https://doi.org/10.1109/TIP.2008.924279

Liang, L.: Image interpolation by blending kernels. IEEE Signal Process. Lett. 15, 805–808 (2008)

Wang, Q., Ward, R.K.: A new orientation-adaptive interpolation method. IEEE Trans. Image Process. 16, 889–900 (2007). https://doi.org/10.1109/TIP.2007.891794

Zhang, L., Wu, X.: An edge-guided image interpolation algorithm via directional filtering and data fusion. IEEE Trans. Image Process. 15, 2226–2238 (2006). https://doi.org/10.1109/TIP.2006.877407

Lin, C., Fan, K., Pu, H., Lu, S., Liang, S.: An HVS-directed neural-network-based image resolution enhancement scheme for image resizing. IEEE Trans. Fuzzy Syst. 15, 605–615 (2007). https://doi.org/10.1109/TFUZZ.2006.889875

Muresan, D.D., Parks, T.W.: Adaptively quadratic (AQua) image interpolation. IEEE Trans. Image Process. 13, 690–698 (2004). https://doi.org/10.1109/TIP.2004.826097

Kim, C.H., Seong, S.M., Lee, J.A., Kim, L.S.: Winscale: an image scaling algorithm using an area pixel model. IEEE Trans. Circuits Syst. Video Technol. 13, 549–553 (2003). https://doi.org/10.1109/TCSVT.2003.813431

Lin, C.C., Wu, Z.C., Tsai, W.K., Sheu, M.H., Chiang, H.K.: The VLSI design of winscale for digital image scaling. In: IIH-MSP 2007-2007 Third International Conference on Intelligent Information Hiding and Multimedia Signal Processing, pp. 511–514 (2007). (IIH-MSP 2007)

Chung-chi, L., Ming-hwa, S., Huann-keng, C., Wen-kai, T., Zeng-chuan, W.: Real-time FPGA architecture of extended linear convolution for digital image scaling. In: 2008 International Conference on Field-Programmable Technology, pp. 381–384 (2008)

Chung-chi, L., Ming-hwa, S., Huann-Keng, C., Chishyan, L., Zeng-chuan, W.: The efficient VLSI design of BI-CUBIC convolution interpolation for digital image processing. In: ISCAS 2008-2008 IEEE International Symposium on Circuits and Systems, pp. 480–483 (2008)

Lin, C., Sheu, M., Chiang, H., Wu, Z., Tu J., Chen, C.: A low-cost VLSI design of extended linear interpolation for real time digital image processing. In: 2008 International Conference on Embedded Software and Systems, pp. 196–202 (2008)

Amanatiadis, A., Andreadis, I., Konstantinidis, K.: Design and implementation of a fuzzy area-based image-scaling technique. IEEE Trans. Instrum. Meas. 57, 1504–1513 (2008). https://doi.org/10.1109/TIM.2008.925723

Chen, P., Lien, C., Lu, C.: VLSI implementation of an edge-oriented image scaling processor. IEEE Trans. Very Large Scale Integr. Syst. 17, 1275–1284 (2009). https://doi.org/10.1109/TVLSI.2008.2003003

Lin, C., Sheu, M., Liaw, C., Chiang, H.: Fast first-order polynomials convolution interpolation for real-time digital image reconstruction. IEEE Trans. Circuits Syst. Video Technol. 20, 1260–1264 (2010). https://doi.org/10.1109/TCSVT.2010.2057017

Chen, S., Huang, H., Luo, C.: A low-cost high-quality adaptive scalar for real-time multimedia applications. IEEE Trans. Circuits Syst. Video Technol. 21, 1600–1611 (2011). https://doi.org/10.1109/TCSVT.2011.2129790

Chen, S.: VLSI implementation of a low-cost high-quality image scaling processor. IEEE Trans. Circuits Syst. II Exp. Briefs 60, 31–35 (2013). https://doi.org/10.1109/TCSII.2012.2234873

Chen, S.: VLSI implementation of an adaptive edge-enhanced image scalar for real-time multimedia applications. IEEE Trans. Circuits Syst. Video Technol. 23, 1510–1522 (2013). https://doi.org/10.1109/TCSVT.2013.2248492

Garg, B., Chaitanya, G.V.N.S.K., Sharma, G.K. A low-cost energy efficient image scaling processor for multimedia applications. In: VDAT 2016-2016 20th International Symposium on VLSI Design and Test, pp. 1–6 (2016)

Sudhakaran, A., Manuel, M.: High-quality image scaling using v-model. In: ICCSDET 2018-2018 International Conference on Circuits and Systems in Digital Enterprise Technology, pp. 1–4 (2018)

Siva, M.V., Jayakumar, E.P.: A low cost high performance VLSI architecture for image scaling in multimedia applications. In: SPIN 2020-2020 7th International Conference on Signal Processing and Integrated Networks, pp. 278–283 (2020)

Siva, M.V., Jayakumar, E.P.: Approximated algorithm and low cost VLSI architecture for edge enhanced image scaling. In: IAICT 2020-2020 IEEE International Conference on Industry 4.0, Artificial Intelligence, and Communications Technology, pp. 125–130 (2020)

sipi misc image dataset. [Online]. https://sipi.usc.edu/database/database.php?volume=misc. Accessed 15 Jan 2022

Zeyde R., Elad M., Protter, M.: On Single Image Scale-Up Using Sparse-Representations. In: Boissonnat, J.D. et al. (eds.) Curves and Surfaces. Curves and Surfaces 2010. Lecture Notes in Computer Science, vol. 6920. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-27413-8_47 (2012)

Kodak Color Image Dataset. [Online]. http://r0k.us/graphics/kodak/. Accessed 27 Feb 2022

Martin, D., Fowlkes, C., Tal D., Malik, J.: A database of human segmented natural images and its application to evaluating segmentation algorithms and measuring ecological statistics. In: ICCV 2001 Proceedings Eighth IEEE International Conference on Computer Vision, pp. 416–423. https://doi.org/10.1109/ICCV.2001.937655.

Acknowledgements

The authors would like to thank SMDP-C2SD Project, NIT Calicut, funded by MeitY, Govt. of India, for providing research facility and technical support.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Midde, V.S., Jayakumar, E.P. Low-cost low-power approximated VLSI architecture for high-quality image scaling in mobile devices. J Real-Time Image Proc 20, 11 (2023). https://doi.org/10.1007/s11554-023-01282-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11554-023-01282-y