Abstract

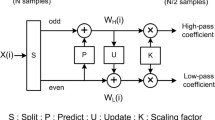

Wavelet transform is an important tool in the field of multimedia signal processing. Due to the growing demand for hardware-based design in the field of image, video, and speech signal processing, several researchers have implemented different discrete wavelet transform (DWT) architectures and measured their performances. In this paper, FPGA implementation of compact and low-power VLSI architectures for one-dimensional and two-dimensional DWT and inverse discrete wavelet transform (IDWT) based on lifting and lattice schemes have been proposed. The adder–subtractor-based design approach has been used to replace the multiplier without affecting the precision. Hardware and timing analysis of existing and proposed 1D and 2D architectures are presented here. The proposed and existing DWT and IDWT architectures are also simulated and synthesized in a Virtex-4 FPGA device. The number of slice LUTs, slice registers, clock frequency, delay, power, and power-LUTs product (PLP) of proposed DWT and IDWT architectures based on lifting and lattice schemes have been found using Xilinx Vivado synthesis tool. The proposed design is also implemented on Basys 3 Artix-7 FPGA board and synthesis results show a significant improvement in terms of area and power compared to other existing architectures.

Similar content being viewed by others

References

Acharya, T.: Intel Corp, Architecture for computing a two-dimensional discrete wavelet transform, U.S. Patent No. 6,178,269, (2001)

Kumar, M.N., Hemanth, J., Prasad, K.D.: VLSI Implementation of DWT Using Systolic Array Architecture. International Journal of Recent Technology and Engineering (IJRTE) 1, 67–73 (2012)

Meher, P.K., Mohanty, B.K., Patra, J.C.: Hardware-efficient systolic-like modular design for two-dimensional discrete wavelet transform. IEEE Transactions on Circuits and Systems II: Express Briefs 55(2), 151–155 (2008)

Daubechies, I., Ten lectures on wavelets. Society for industrial and applied mathematics, (1992)

Jana, J., Tripathi, S., Chowdhury, R.S., Bhattacharya, A., Bhaumik, J.: Efficient, an area, architecture, V.L.S.I., for 1-D and 2-D discrete wavelet transform (DWT) and inverse discrete wavelet transform (IDWT). Dev. Integr. Circuit IEEE 2021, 378–382 (2021)

Liao, H., Mandal, M.K., Cockburn, B.F.: Efficient architectures for 1-D and 2-D lifting-based wavelet transforms. IEEE Trans. Signal Process. 52(5), 1315–1326 (2004)

Bamerni, S.A., Al-Sulaifanie, A.K.: An efficient non-separable architecture for Haar wavelet transform with lifting structure. Microprocess. Microsyst. 71, 102881 (2019)

Maye, G.K., Srinivasulu, T.: VLSI architecture for coherent 9, 7 lifting based 2D-discrete wavelet transform. Ann. IEEE India Conf. IEEE 2015, 1–6 (2015)

Darji, A.D., Limaye, A.: Memory efficient VLSI architecture for lifting-based DWT, In,: IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE 2014, 189–192 (2014)

Borra, S.P.R., Panakala, R.K., Kumar, P.R.: VLSI implementation of image fusion using DWT-PCA algorithm with maximum selection rule. Int. J. Intell. Eng. Syst. 12(5), 1–11 (2019)

Zhang, W., Wu, C., Zhang, P., Liu, Y.: An internal folded hardware-efficient architecture for lifting-based multi-level 2-D 9/7 DWT. Appl. Sci. 9(21), 4635 (2019)

Maye, G.K., Srinivasulu, T.: Level Skip VLSI Architecture for 2D-Discrete Wavelet Transform, In Innovations in Computer Science and Engineering, Springer, Singapore, (2017), pp. 347–353

Srinivasarao, B.K.N., Chakrabarti, I.: High performance VLSI architecture for 3-D discrete wavelet transform, In,: International Symposium on VLSI Design, Automation and Test (VLSI-DAT). IEEE 2016, 1–4 (2016)

Stokfiszewski, K., Wieloch, K., Yatsymirskyy, M.: An efficient implementation of one-dimensional discrete wavelet transform algorithms for GPU architectures. J. Supercomput. 78, 11539–63 (2022)

Xiong, C., Tian, J., Liu, J.: Efficient architectures for two-dimensional discrete wavelet transform using lifting scheme. IEEE Trans. Image Process. 16(3), 607–614 (2007)

Pande, A., Zambreno, J.: A reconfigurable architecture for secure multimedia delivery, In 2010 23rd International Conference on VLSI Design, IEEE, (2010), pp. 258–263

Farghaly, S.H., Ismail, S.M.: Floating-point discrete wavelet transform-based image compression on FPGA. AEU-Int. J. Electron. Commun. 124, 153363 (2020)

Dahiya, V., Singhal, M., Joshi, A.: Multiplier less high speed VLSI architecture for lifting based 1-D discrete wavelet transform, In 2016 International Conference on Recent Advances and Innovations in Engineering (ICRAIE), IEEE, (2016), pp. 1–5

Hajjaji, M.A., Gafsi, M., Ben Abdelali, A., Mtibaa, A.: FPGA implementation of digital images watermarking system based on discrete Haar wavelet transform, Security and Communication Networks, (2019)

Mishra, A., Mahapatra, S., Banerjee, S.: Modified Frei-Chen operator-based infrared and visible sensor image fusion for real-time applications. IEEE Sens. J. 17(14), 4639–4646 (2017)

Pemmaraju, M., Mashetty, S.C., Aruva, S., Saduvelly, M., Edara, B.B.: Implementation of image fusion based on wavelet domain using FPGA, In 2017 International Conference on Trends in Electronics and Informatics (ICEI), IEEE, (2017), pp. 500–504

University of Southern California, “The USC-SIPI Image Database”. http://sipi.usc.edu/database/database.php. Accessed 05 (2023)

Loughborough University, “Uncompressed Colour Image Database”. http://jasoncantarella.com/downloads/ucid.v2.tar.gz. Accessed 05 (2023)

Eastman Kodak Company, “Kodak Lossless True Color Image Suite Database”. http://r0k.us/graphics/kodak/. Accessed 05 (2023)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jana, J., Chowdhury, R.S., Tripathi, S. et al. FPGA implementation of compact and low-power multiplierless architectures for DWT and IDWT. J Real-Time Image Proc 21, 19 (2024). https://doi.org/10.1007/s11554-023-01396-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11554-023-01396-3