Abstract

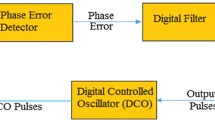

Nowadays, the modern microelectronics digital communication systems are using low power and efficient design for wide variety of applications in real world. Recent researchers focusing on amplifier circuits for increasing applications with novel designs; conventional method uses FinFET CMOS design, and other reconfigurable designs, which consumes much power on designing and to overcome the design complexity of existing work, the proposed optimal power reduction strategy is employed on the ADC lock-in amplifier. Here the two stage lock-in amplifier is constructed with gated clocking of DFF switching strategy to reduce the power consumption and to obtain better results than previous works. Virtext FPGA model of amplifier is designed with Xilinx ISE 14.2 tool. The design of lock-in Amplifier has both sensing stage and latch stage with better sampling periods of edge triggering state, which improves the performance. High speed FPGA with mixed signal processing application is capable for this design. Experimental results analyzed with the power, area and delay as major concern and switching state with clocking model determines the high speed design. By comparing with the previous work, the proposed work is designed to achieve better results.

Similar content being viewed by others

References

Aguirre J, García-Romeo D, Medrano N et al (2014) Square-signal-based algorithm for analog lock-in amplifiers. IEEE Trans Ind Electron 61(10):5590–5598

Ayat M, Karami MA, Mirzakuchaki S, Beheshti SA (2016) Design of multiple modulated frequency lock-in amplifier for tapping-mode atomic force microscopy systems. IEEE Trans Instrum Meas 65:2284–2292. https://doi.org/10.1109/TIM.2016.2579438

Ayat M, Karami MA, Mirzakuchaki S, Beheshti-Shirazi A (2016) Design of multiple modulated frequency lock-in amplifier for tapping-mode atomic force microscopy systems. IEEE Trans Instrum Meas 65(10):2284–2292

Chen S-WM, Brodersen RW (2006) A 6b 600MS/s 5.3mW asynchronous ADC in 0.13 μm CMOS. In: IEEE 2006 international solid state circuits conference digest of technical papers, pp 2350–2359

De Marcellis A, Ferri G, D’Amico A (2016) One-decade frequency range, in-phase auto-aligned 1.8 V 2 mW fully analog CMOS integrated lock-in amplifier for small/noisy signal detection. IEEE Sens J 16(14):5690–5701

Dezhi X, Yan Z, Chi-Hang C, Franco M, Seng-Pan U, Rui Paulo M (2018) Design of a high speed time interleaved sub-ranging SAR ADC with optimal code transfer technique. IEEE Trans Circuits Syst

Dorrington AA, Rainer K (2012) A Simple microcontroller based digital lock-in amplifier for the detection of low level optical signals. In: Proceedings of the IEEE international workshop on electronic design, test and applications

Gervasoni G, Carminati M, Ferrari G (2017) Switched ratiometric lock-in amplifier enabling sub-ppm measurements in a wide frequency range. Rev Sci Instrum 88:104704. https://doi.org/10.1063/1.4996423

Giaconia GC, Greco G, Mistretta L, Rizzo R (2017) Exploring FPGA-based lock-in techniques for brain monitoring applications. Electronics 6:18

Han X, Ding P, Xie J, Shi J, Li L (2012) Precise measurement of the inductance and resistance of a pulsed field magnet based on digital lock-in technique. IEEE Trans Appl Superconduct 22(3):9001105

Hu A, Vamsy PC (2010) CMOS optoelectronic lock-in amplifier with integrated phototransistor array. IEEE Trans Biomed Circuits Syst 4(5):274–280

Im J, Zheng K, Chou CH, Zhou L, Kim JW, Chen S, Wang Y, Hung HW, Tan K, Lin W, Roldan AB (2020) A 112-Gb/s PAM-4 long-reach wireline transceiver using a 36-way time-interleaved SAR ADC and inverter-based RX analog front-end in 7-nm FinFET. IEEE J Solid-State Circuits 56(1):7–18

Kan H, Yangy G, Xibin Z, Dihu C, Zhigang C, Min W, Zhen Z, Zixin W (2019) A Wide band digital lock-in amplifier and its application in microfluidic impedance measurement. Sensors 19(16):3519. (10.3390%2Fs19163519)

Kaushal K, Akbar SA (2020) Evolution of lock-in amplifier as portable sensor interface platform: a review. IEEE Sens J 20(18):10345–10354

Lim W, Kang H, Lee W, Bae J, Oh S, Oh H, Chae S, Hwang KC, Lee KY, Yang Y (2018) Dual-mode CMOS power amplifier based on load-impedance modulation. IEEE Microwave Wirel Compon Lett 28(11):1041–1043

Lioe DX, Mars K, Kawahito S, Yasutomi K, Kagawa K, Yamada T, Hashimoto M (2016) A stimulated Raman scattering CMOS pixel using a high-speed charge modulator and lock-in amplifier. Sensors 16:532. https://doi.org/10.3390/s16040532

Maya-Hernández PM, Sanz-Pascual MT, Calvo B (2015) CMOS low-power lock-in amplifiers with signal rectification in current domain. IEEE Trans Instrum Meas 64(7):1858–1867

Nahid M, Gyung-Su B (2018) An optimal design methodology for yield-improved and low power pipelined ADC. IEEE Trans Semicond Manuf 31(1):130–135

Sabyasachi B, Ragib N A, Basab BP, Kaustubh B (2016) Implementation of digital lock-in amplifier. In: IUPAP conference on computational physics conference series, pp 759. https://doi.org/10.1088/1742-6596/759/1/012096

Sarith M, Janak Rani M, Anand M (2020) A 45nm CMOS power amplifier with reconfigurable gain and improved linearity. J Adv Res Dyn Control Syst 12(6):387–396

Schubert M (1997) Operational amplifier modeling using event-driven VHDL. BMAS Workshop, Orlando, FL, USA. 20–21 October 1997

Shende RM, Gumble PR (2011) VLSI Design of low power high speed 4 Bit Resolution pipeline ADC in submicron CMOS Technology. Int J VLSI Des Commun Syst 2(4):81–93

Shirane T, Ito M (2012) Measurement of hysteresis loop on soft magnetic materials using lock-in amplifier. IEEE Trans Magn 48(4):1437–1440

Sissons BR (2014) Developing a tool for generation of operational amplifier models from datasheet parameters. Thesis submitted to university of arkansas, fayetteville

Sonnaillon MO, Urteaga R, Bonetto FJ (2008) High-frequency digital lock-in amplifier using random sampling. IEEE Trans Instrum Meas 57(3):616–621

Zhang C, Liu H, Ge J, Dong H (2020) FPGA-based digital lock-in amplifier with high-precision automatic frequency tracking. IEEE Access 8:123114–123122

Funding

The authors have no relevant financial or non-financial interests to disclose.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have no conflicts of interest to declare that are relevant to the content of this article. All authors certify that they have no affiliations with or involvement in any organization or entity with any financial interest or non-financial interest in the subject matter or materials discussed in this manuscript. The authors have no financial or proprietary interests in any material discussed in this article.

Ethical approval

The research not involving any human participants and/or animals.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Saritha, M., Lavanya, M., Ajitha, G. et al. A VLSI design of clock gated technique based ADC lock-in amplifier. Int J Syst Assur Eng Manag 13, 2743–2750 (2022). https://doi.org/10.1007/s13198-022-01747-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13198-022-01747-6