Abstract

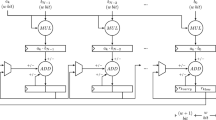

The number theoretic transform (NTT) is used to efficiently execute polynomial multiplication. It has become an important part of lattice-based post-quantum methods and the subsequent generation of standard cryptographic systems. However, implementing post-quantum schemes is challenging since they rely on intricate structures. This paper demonstrates how to develop a high-speed NTT multiplier highly optimized for FPGAs with few logical resources. We describe a novel architecture for NTT that leverages unique precomputation. Our method efficiently maps these specific pre-computed values into the built-in Block RAMs, which greatly reduces the area and time required for implementation when compared to previous works. We have chosen Kyber parameters to implement the proposed architectures. Compared to the most well-known approach for implementing Kyber’s polynomial multiplication using NTT, the AC (area \(\times \) latency) is reduced by \(33\%\), and AT (area \(\times \) time) is improved by \(18\%\) as a result of the pre-computation we suggest in this study.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.References

Göttert, N., Feller, T., Schneider, M., Buchmann, J., Huss, S.A.: On the design of hardware building blocks for modern lattice-based encryption schemes. CHES 7428, 512–529 (2012)

Pöppelmann, T., Güneysu, T.: Towards efficient arithmetic for lattice-based cryptography on reconfigurable hardware. LATINCRYPT 7533, 139–158 (2012)

Pöppelmann, T., Güneysu, T.: Towards practical lattice-based public-key encryption on reconfigurable hardware. Sel. Areas Cryptogr. 8282, 68–85 (2013)

Aysu, A., Patterson, C., Schaumont, P.: Low-cost and area-efficient FPGA implementations of lattice-based cryptography. In: HOST, pp. 81–86 (2013)

Roy, S.S., Vercauteren, F., Mentens, N., Chen, D.D., Verbauwhede, I.: Compact ring-LWE cryptoprocessor. CHES 8731, 371–391 (2014)

Zhang, N., Yang, B., Chen, C., Yin, S., Wei, S., Liu, L.: Highly efficient architecture of Newhope-NIST on FPGA using low-complexity NTT/INTT. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2020(2), 49–72 (2020)

Longa, P., Naehrig, M.: Speeding up the number theoretic transform for faster ideal lattice-based cryptography. CANS 10052, 124–139 (2016)

Banerjee, U., Ukyab, T.S., Chandrakasan, A.P.: Sapphire: a configurable crypto-processor for post-quantum lattice-based protocols. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2019(4), 17–61 (2019)

Chen, Z., Ma, Y., Chen, T., Lin, J., Jing, J.: Towards efficient Kyber on FPGAS: a processor for vector of polynomials. In: ASP-DAC, pp. 247–252 (2020)

Mert, A.C., Karabulut, E., Öztürk, E., Savas, E., Becchi, M., Aysu, A.: A flexible and scalable NTT hardware : applications from homomorphically encrypted deep learning to post-quantum cryptography. In: DATE, pp. 346–351 (2020)

Mert, A.C., Karabulut, E., Öztürk, E., Savas, E., Aysu, A.: An extensive study of flexible design methods for the number theoretic transform. IEEE Trans. Comput. 71(11), 2829–2843 (2022)

Karabulut, E., Aysu, A.: RANTT: A RISC-V architecture extension for the number theoretic transform. In: FPL, pp. 26–32 (2020)

Fritzmann, T., Sepúlveda, J.: Efficient and flexible low-power NTT for lattice-based cryptography. In: HOST, pp. 141–150 (2019)

Xing, Y., Li, S.: An efficient implementation of the newhope key exchange on FPGAS. IEEE Trans. Circuits Syst. I Regul. Pap. 67–I(3), 866–878 (2020)

Du, C., Bai, G., Wu, X.: High-speed polynomial multiplier architecture for ring-LWE based public key cryptosystems. In: ACM Great Lakes Symposium on VLSI, pp. 9–14 (2016)

Kuo, P., Chen, Y., Hsu, Y., Cheng, C., Li, W., Yang, B.: High performance post-quantum key exchange on FPGAS. J. Inf. Sci. Eng. 38(4), 1211–1229 (2022)

Nguyen, D.T., Dang, V.B., Gaj, K.: A high-level synthesis approach to the software/hardware codesign of NTT-based post-quantum cryptography algorithms. In: FPT, pp. 371–374 (2019)

Nguyen, D.T., Dang, V.B., Gaj, K.: High-level synthesis in implementing and benchmarking number theoretic transform in lattice-based post-quantum cryptography using software/hardware codesign. ARC Lecture Notes Comput. Sci. 12083, 247–257 (2020)

Di Matteo, S., Gerfo, M.L., Saponara, S.: VLSI design and FPGA implementation of an NTT hardware accelerator for homomorphic seal-embedded library. IEEE Access 11, 72498–72508 (2023)

Shahmirzadi, A.R., Bozilov, D., Moradi, A.: New first-order secure AES performance records. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2021(2), 304–327 (2021)

Morales-Sandoval, M., Flores, L.A.R., Cumplido, R., Garcia-Hernandez, J.J., Feregrino, C., Algredo-Badillo, I.: A compact FPGA-based accelerator for curve-based cryptography in wireless sensor networks. J. Sensors 2021, 8860413–1886041313 (2021)

Avanzi, R., Bos, J., Ducas, L., Kiltz, E., Lepoint, T., Lyubashevsky, V., Schanck, J.M., Schwabe, P., Seiler, G., Stehlé, D.: Crystals-kyber algorithm specifications and supporting documentation. NIST PQC Round 2(4), 1–43 (2017)

Pöppelmann, T., Oder, T., Güneysu, T.: High-performance ideal lattice-based cryptography on 8-bit ATxmega microcontrollers. LATINCRYPT 9230, 346–365 (2015)

Bisheh-Niasar, M., Azarderakhsh, R., Mozaffari-Kermani, M.: High-speed ntt-based polynomial multiplication accelerator for post-quantum cryptography. In: 2021 IEEE 28th symposium on computer arithmetic (ARITH), pp. 94–101. IEEE (2021)

Alkim, E., Evkan, H., Lahr, N., Niederhagen, R., Petri, R.: ISA extensions for finite field arithmetic accelerating Kyber and newhope on RISC-V. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2020(3), 219–242 (2020)

Huang, Y., Huang, M., Lei, Z., Wu, J.: A pure hardware implementation of CRYSTALS-KYBER PQC algorithm through resource reuse. IEICE Electron. Express 17(17), 20200234 (2020)

Fritzmann, T., Sigl, G., Sepúlveda, J.: RISQ-V: tightly coupled RISC-V accelerators for post-quantum cryptography. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2020(4), 239–280 (2020)

Xing, Y., Li, S.: A compact hardware implementation of CCA-secure key exchange mechanism CRYSTALS-KYBER on FPGA. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2021(2), 328–356 (2021)

Yaman, F., Mert, A.C., Öztürk, E., Savaş, E.: A hardware accelerator for polynomial multiplication operation of crystals-kyber pqc scheme. In: 2021 design, automation & test in Europe conference & exhibition (DATE), pp. 1020–1025 (2021)

Ni, Z., Khalid, A., Liu, W., O’Neill, M.: Towards a lightweight crystals-kyber in FPGAS: an ultra-lightweight bram-free ntt core. In: IEEE international symposium on circuits and systems (ISCAS), IEEE (2023)

Zhang, C., Liu, D., Liu, X., Zou, X., Niu, G., Liu, B., Jiang, Q.: Towards efficient hardware implementation of NTT for Kyber on FPGAS. In: 2021 IEEE international symposium on circuits and systems (ISCAS), pp. 1–5. IEEE (2021)

Author information

Authors and Affiliations

Contributions

Raziyeh Salarifard and Hadi soleimany wrote the main manuscript, prepared figures and tables, and reviewed the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Salarifard, R., Soleimany, H. An efficient hardware accelerator for NTT-based polynomial multiplication using FPGA. J Cryptogr Eng 14, 415–426 (2024). https://doi.org/10.1007/s13389-024-00357-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13389-024-00357-1