Abstract

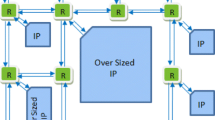

Congestion aware routing algorithm enhanced the Network on Chip (NoC) performance and power consumption. The main assignment to reach this goal is to select the most proper congestion parameters along with the accuracy of collecting the congestion data. Congestion detection can be perceived while monitoring the network resources (for example monitoring the free buffers of nodes) or predicting the network traffic injection rate. The network monitoring has communication overheads as the number of nodes extend, and predicting the traffic injection rate has communication overhead along with processing overhead. In a congestion aware routing algorithm, after determining possible paths, the selection function chooses a path among the suggested ones, using the congestion detection function. In this paper, congestion detection investigates the free resources of the next cluster (neighbor). This method is distinguished in two phases. In the first phase, candidate paths will be selected by a minimal adaptive algorithm, and in the next phase, the cluster’s congestion information will be sent to the selected node in order to select the best path among the suggested paths. There has been no extra signal added to the network to transfer the congestion information. In order to ensure deadlock freedom of the routing algorithm, turn restriction and virtual channels are used. Experimental results can clearly prove the improvements of average delay and network performance, whereas the average delay is reduced by 13% and 2.5% based on the traffic patterns used, and network performance gained 9% and 57% direct improvement on the algorithm output.

Similar content being viewed by others

References

Akbar, R., Safaei, F.: a novel congestion-aware and adaptive routing algorithm in mesh-based networks-on-chip with segmentation. In: 19th International Symposium on Computer Architecture and Digital Systems (CADS). (2017)

Akbar, R., Safaei, F., Modallalkar, S.M.S.: A novel power efficient adaptive RED-based flow control mechanism for networks-on-chip. Comput. Electr. Eng. 51, 121–138 (2016)

Benmessaoud, G.A., Bomel, P., Sevaux, M.: Application-aware multi-objective routing based on genetic algorithm for 2D network-on-chip. Microprocess. Microsyst. 61, 135–153 (2018)

Duato, J., Yalamanchili, S., Ni, L.: Interconnection networks. Morgan Kaufmann, Burlington (2003)

Fu, B., Kim, J.: Footprint: regulating routing adaptiveness in networks-on-chip. In: ACM SIGARCH Computer Architecture News, ACM, vol. 45, no. 2, pp. 691–702. (2017)

Gratz, P., Grot, B., Keckler, S.W.: Regional congestion awareness for load balance in networks-on-chip. In: Proceeding of international symposium on high-performance computer architecture, pp. 203–214. (2008)

Hu, J.H.J., Marculescu, R.: DyAD: smart routing for networks-on-chip. In: Proceedings design automation conference, pp. 260–263. (2004)

Jin, K., Li, C., Dong, D., Fu, B.: HARE: history-aware adaptive routing algorithm for endpoint congestion in networks-on-chip. Int. J. Parallel Prog. 47, 433–450 (2019)

Kai-Yuan, J., Chao, C.H., Wang, H.Y., Wu, A.Y.: Traffic-thermal mutual-coupling cosimulation platform for three-dimensional networkon-chip. In: IEEE International Symposium on V LSI Design, Automation, and Test (V LSI-DATlO), pp. 135–138. (2010)

Kim, G., Kim, C., Jeong, J., Parker, M., Kim, J.: Contention-based congestion management in large-scale networks. In: 2016 49th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), IEEE, pp. 1–13. (2016)

Li, M., Zeng, Q.A., Jone, W.B.: DyXY: a proximity congestion-aware deadlock-free dynamic routing method for network on chip. In: ACM/IEEE design automation conference, pp. 849–852. (2006)

Ma, S., Jerger, N.E., Wang, Z.: DBAR: an efficient routing algorithm to support multiple concurrent applications in networks-on-chip categories and subject descriptors. In: International symposium on computer architecture (ISCA). (2011)

Maky, T., Wang, X., Agyemen, M.O., Zong, W.: Unbiased regional congestion aware selection function for nocs. In: 9th International Symposium on Networks-on-Chip, pp. 19–26. (2015)

Towles, B., Dally, W.J.: Route packets, not wires: on-chip interconnection networks. In: The 38th Design Automation Conference, LasVegas, NV, USA, USA: IEEE, pp. 684–689. (2001)

Xie, R., Cai, J., Xin, X., Yang, B.: LBFT: a fault-tolerant routing algorithm for load-balancing network-on-chip based on odd–even turn model. J. Supercomput. 74(8), 3726–3747 (2018)

Xu, S., Wu, J., Fu, B., Chen, M., Zhang, L.: Efficient Regional Congestion Awareness (ERCA) for load balance with aggregated congestion information. In: 25th Euromicro International Conference on Parallel, Distributed and Network-Based Processing, pp. 93–94. (2017)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bahman, F., Reza, A., Reshadi, M. et al. CACBR: Congestion Aware Cluster Buffer base routing algorithm with minimal cost on NOC. CCF Trans. HPC 2, 297–306 (2020). https://doi.org/10.1007/s42514-020-00027-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42514-020-00027-8