Abstract

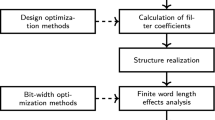

The most advanced techniques in the design of multiplierless finite impulse response (FIR) filters explore common subexpression sharing when the filter coefficients are optimized. Existing techniques, however, either suffer from a heavy computational overhead, or have no guarantees on the minimal hardware cost in terms of the number of adders. A recent technique capable of designing long filters optimizes filter coefficients in pre-specified subexpression spaces. The pre-specified subexpression spaces determine if a filter with fewer adders may be achieved. Unfortunately, there is no known technique that can find subexpression spaces that can guarantee the solution with the minimum number of adders in the implementation. In this paper, a tree search algorithm is proposed to update and expand the subexpression spaces dynamically, and thus, to achieve the maximum subexpression sharing during the optimization. Numerical examples show that the proposed algorithm generates filters using fewer adders than other non-optimum algorithms. On the other hand, as a consequence of its efficiency, our proposed technique is able to design longer filters than the global optimum algorithm.

Similar content being viewed by others

References

N. Boullis, T. Tisserand, Some optimizations of hardware multiplication by constant matrices. IEEE Trans. Comput. 54, 1271–1282 (2005)

D.R. Bull, D.H. Horrocks, Primitive operator digital filters. IEE Proc. G 138, 401–412 (1991)

A.G. Dempster, M.D. Macleod, Use of minimum-adder multiplier blocks in FIR digital filters. IEEE Trans. Circuits Syst. II 42, 569–577 (1995)

O. Gustafsson, A difference based adder graph heuristic for multiple constant multiplication problems, in Proc. IEEE ISCAS’07, New Orleans, LA, 2007, pp. 1097–1100

O. Gustafsson, Lower bounds for constant multiplication problems. IEEE Trans. Circuits Syst. II 54, 974–978 (2007)

O. Gustafsson, L. Wanhammar, Design of linear-phase FIR filters combining subexpression sharing with MILP, in Proc. MWSCAS’02, 2002, pp. 9–12

O. Gustafsson, L. Wanhammar, ILP modeling of the common subexpression sharing problem, in Proc. IEEE ICECS’02, Dubrovnic, Croatia, 2002, pp. 1171–1174

R.I. Hartley, Subexpression sharing in filters using canonic signed digit multipliers. IEEE Trans. Circuits Syst. II 43, 677–688 (1996)

B.-R. Horng, H. Samueli, Willson, Jr., A.N., The design of two-channel lattice structure perfect-reconstruction filter banks using power-of-two coefficients. IEEE Trans. Circuits Syst. I 40, 497–499 (1993)

H.-J. Kang, I.-C. Park, FIR filter synthesis algorithms for minimizing the delay and the number of adders. IEEE Trans. Circuits Syst. II 48, 770–777 (2001)

D.M. Kodek, Design of optimal finite wordlength FIR digital filters using integer programming techniques. IEEE Trans. Acoust. Speech Signal Process. ASSP-28, 304–308 (1980)

Y.C. Lim, Design of discrete-coefficient-value linear phase FIR filters with optimum normalized peak ripple magnitude. IEEE Trans. Circuits Syst. 37, 1480–1486 (1990)

Y.C. Lim, S.R. Parker, Discrete coefficient FIR digital filter design based upon an LMS criteria. IEEE Trans. Circuits Syst. 30, 723–739 (1983)

Y.C. Lim, S.R. Parker, FIR filter design over a discrete power-of-two coefficient space. IEEE Trans. Acoust. Speech Signal Process. ASSP-31, 583–591 (1983)

Y.C. Lim, R. Yang, D.N. Li, J.J. Song, Signed power-of-two term allocation scheme for the design of digital filters. IEEE Trans. Circuits Syst. II 46, 577–584 (1999)

Y.C. Lim, Y.J. Yu, A width-recursive depth-first tree search approach for the design of discrete coefficient perfect reconstruction lattice filter bank. IEEE Trans. Circuits Syst. II 50, 257–266 (2003)

K. Nakayama, Permuted difference coefficient realization of FIR digital filters. IEEE Trans. Acoust. Speech Signal Process. ASSP-30, 269–278 (1982)

M. Potkonjak, M.B. Shrivasta, A.P. Chandrakasan, Multiple constant multiplication: Efficient and versatile framework and algorithms for exploring common subexpression elimination. IEEE Trans. Comput. Aided Des. 15, 151–161 (1996)

H. Samueli, An improved search algorithm for the design of multiplierless FIR filters with powers-of-two coefficients. IEEE Trans. Circuits Syst. 36, 1044–1047 (1989)

A.P. Vinod, E.M.-K. Lai, A.B. Premkuntar, C.T. Lau, FIR filter implementation by efficient sharing of horizontal and vertical common subexpressions. Electron. Lett. 39, 251–253 (2003)

Y. Voronenko, M. Püschel, Multiplierless multiple constant multiplication. ACM Trans. Algorithms 3, 1–38 (2007)

Y. Wang, K. Roy, CSDC: A new complexity reduction technique for multiplierless implementation of digital FIR filters. IEEE Trans. Circuits Syst. I 52, 1845–1853 (2005)

F. Xu, C.-H Chang, C.-C. Jong, Contention resolution algorithm for common subexpression elimination in digital filter design. IEEE Trans. Circuits Syst. II 52, 695–700 (2005)

F. Xu, C.-H Chang, C.-C. Jong, Design of low-complexity FIR filters based on signed-powers-of-two coefficients with reusable common subexpressions. IEEE Trans. Comput. Aided Des. 26, 1898–1907 (2007)

J. Yli-Kaakinen, T. Saramäki, A systematic algorithm for the design of multiplierless FIR filters, in Proc. IEEE ISCAS’01, Sydney, Australia, 2001, pp. 185–188

Y.J. Yu, Y.C. Lim, A novel genetic algorithm for the design of a signed power-of-two coefficient quadrature mirror filter lattice filter bank. Circuit Syst. Signal Process. 21, 263–276 (2002)

Y.J. Yu, Y.C. Lim, Design of linear phase FIR filters in subexpression space using mixed integer linear programming. IEEE Trans. Circuits Syst. I 54, 2330–2338 (2007)

Y.J. Yu, Y.C. Lim, Roundoff noise analysis of signals represented using signed power-of-two terms. IEEE Trans. Signal Processing 55, 2122–2135 (2007)

Author information

Authors and Affiliations

Corresponding author

Additional information

This project is supported in part by Nanyang Technological University (NTU) Research Grant COE-SUG (1) and Temasek Laboratory @ NTU.

Rights and permissions

About this article

Cite this article

Yu, Y.J., Lim, Y.C. Optimization of Linear Phase FIR Filters in Dynamically Expanding Subexpression Space. Circuits Syst Signal Process 29, 65–80 (2010). https://doi.org/10.1007/s00034-009-9114-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-009-9114-7