Abstract

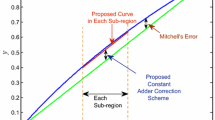

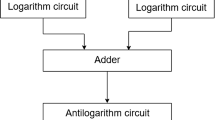

This paper presents a decimal logarithmic converter based on the decimal first-order polynomial (linear) approximation algorithm. The proposed approach is mainly based on a look-up table, followed a decimal linear approximation step. Compared with a binary-based decimal linear approximation algorithm (Algorithm 1), the proposed algorithm (Algorithm 2) is error-free in the conversion between the decimal and the binary formats. The proposed architecture is implemented by the combinational logic in the binary coded decimal (BCD) encoding on Virtex5 XC5VLX110T FPGA. The results of the comparison show that the hardware performance of Algorithm 2 can run 2.15 times faster than Algorithm 1, with the expense of 1.14 times more area.

Similar content being viewed by others

References

K.H. Abed, R.E. Siferd, CMOS VLSI implementation of a low-power logarithmic converter. IEEE Trans. Comput. 52(11), 1421–1433 (2003)

D. Chen, Y. Choi, L. Chen, D. Teng, K. Wahid, S. Ko, A novel decimal-to-decimal logarithmic converter, in Proceedings of 2008 IEEE International Symposium on Circuit and System, Seattle, USA (2008), pp. 688–691

M. Combet, H. Van Zonneveld, L. Verbeek, Computation of the base two logarithm of binary numbers. IEEE Trans. Electron. Comput. 14, 863–867 (1965)

M.F. Cowlishaw, Decimal floating-point: algorithm for computers, in Proceedings of 16th IEEE Symposium on Computer Arithmetic, Washington, USA (2003), pp. 104–111

J.-P. Deschamps, G.J.A. Bioul, G.D. Sutter, Synthesis of Arithmetic Circuits: FPGA, ASIC and Embedded Systems (Wiley, Hoboken, 2006)

M.A. Erle, M.J. Schulte, Decimal multiplication via carry-save addition, in Proceedings of 2003 IEEE International Conference on Application-Specific Systems, Architectures, and Processors, The Hague, The Netherlands (2003), pp. 348–358

E.L. Hall, D.D. Lynch, S.J. Dwyer, Generation of products and quotients using approximate binary logarithms for digital filtering applications. IEEE Trans. Comput. 19, 97–105 (1970)

IEEE, Inc., IEEE 754-2008 Standard for Floating-point Arithmetic (2008)

T. Lang, A. Nannarelli, A radix-10 combinational multiplier, in Proceedings of IEEE 40th Asilomar Conference on Signals, Systems and Computers, Pacific Grove, USA (2006), pp. 313–317

J.N. Mitchell, Computer multiplication and division using binary logarithms. IRE Trans. Electron. Comput. 11, 512–517 (1962)

J.M. Muller, Elementary Functions, Algorithms and Implementation (Birkhauser, Boston, 2005)

S.L. SanGregory, R.E. Siferd, C. Brother, D. Gallagher, A fast, low-power logarithm approximation with CMOS VLSI implementation, in Proceedings of IEEE 42nd Midwest Symposium on Circuits and Systems. Las Cruces, USA (1999), pp. 388–391

T. Sasao, S. Nagayama, J.T. Butler, Numerical function generators using LUT cascades. IEEE Trans. Comput. 56(6), 826–838 (2007)

Xilinx Inc., Xilinx University Program XUPV5-LX110T Development System. Hardware Reference Manual (2009)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chen, D., Ko, SB. A Novel Decimal Logarithmic Converter Based on First-Order Polynomial Approximation. Circuits Syst Signal Process 31, 1179–1190 (2012). https://doi.org/10.1007/s00034-011-9365-y

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-011-9365-y