Abstract

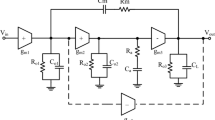

In this paper, a dual-Miller parallel compensation (DMPC) technique for low-power three-stage amplifier is presented with detailed theoretical analysis. A feedback network realized by capacitor and transconductance is added between the first and third stage, which improves significantly the performance when driving large capacitive loads. Furthermore, it is found to be stable for a wide range of capacitive loads. The proposed DMPC amplifier has been implemented in a 0.13-μm CMOS process and the chip area is 0.17×0.11 mm2. It achieves a 0.87 MHz gain-bandwidth product by consuming a total current of 41 μA. The DMPC amplifier is verified to be stable when the load capacitor ranges from 8 pF to 2 nF.

Similar content being viewed by others

References

P.E. Allen, D.R. Holberg, CMOS Analog Circuit Design, 2nd edn. (Oxford University, Oxford, 2002)

S.S. Chong, P.K. Chan, Cross feedforward cascode compensation for low-power three-stage amplifier with large capacitive load. IEEE J. Solid-State Circuits 47, 1–8 (2012)

R.G.H. Eschauzier, J.H. Huijsing, Frequency Compensation Techniques for Low-Power Operational Amplifiers (Kluwer, Boston, 1995)

R.G.H. Eschauzier, L.P.T. Kerklaan, J.H. Huijsing, A 100-MHz 100-dB operational amplifier with multipath nested Miller compensation structure. IEEE J. Solid-State Circuits 27, 1709–1717 (1992)

R.G.H. Eschauzier, R. Hogervorst, J.H. Huijsing, A programmable 1.5 V CMOS class-AB operational amplifier with hybrid nested Miller compensation for 120 dB gain and 6 MHz UGF. IEEE J. Solid-State Circuits 29, 1497–1504 (1994)

X. Fan, C. Mishra, E. Sánchez-Sinencio, Single Miller capacitor frequency compensation technique for low-power multistage amplifiers. IEEE J. Solid-State Circuits 40, 584–592 (2005)

A.D. Grasso, D. Marano, G. Palumbo, S. Pennisi, Improved reversed nested Miller compensation technique with voltage buffer and nulling resistor. IEEE Trans. Circuits Syst. II 54, 382–386 (2007)

A.D. Grasso, G. Palumbo, S. Pennisi, Advances in reversed nested Miller compensation. IEEE Trans. Circuits Syst. I 54, 1459–1470 (2007)

S. Guo, H. Lee, Single-capacitor active-feedback compensation for small-capacitive-load three-stage amplifiers. IEEE Trans. Circuits Syst. II 56, 758–762 (2009)

S. Guo, H. Lee, Dual active-capacitive-feedback compensation for low-power large-capacitive-load three-stage amplifiers. IEEE J. Solid-State Circuits 46, 452–464 (2011)

K.P. Ho, C.F. Chan, C.S. Choy, K.P. Pun, Reversed nested Miller compensation with voltage buffer and nulling resistor. IEEE J. Solid-State Circuits 38, 1735–1738 (2003)

J.H. Huijsing, Operational Amplifier—Theory and Design, 2nd edn. (Springer, Berlin, 2011)

Y.B. Kamath, R.G. Meyer, P.R. Gray, Relationship between frequency response and settling time of operational amplifiers. IEEE J. Solid-State Circuits 9, 347–352 (1974)

H. Lee, P.K.T. Mok, Active-feedback frequency-compensation technique for low-power multistage amplifiers. IEEE J. Solid-State Circuits 38, 511–520 (2003)

H. Lee, P.K.T. Mok, Advances in active-feedback frequency compensation with power optimization and transient improvement. IEEE Trans. Circuits Syst. I 51, 1690–1696 (2004)

H. Lee, K.N. Leung, P.K.T. Mok, A dual-path bandwidth extension amplifier topology with dual-loop parallel compensation. IEEE J. Solid-State Circuits 38, 1739–1744 (2003)

K.N. Leung, P.K.T. Mok, Analysis of multistage amplifier-frequency compensation. IEEE Trans. Circuits Syst. I 48, 1041–1056 (2001)

K.N. Leung, P.K.T. Mok, W.H. Ki, J.K.O. Sin, Three-stage large capacitive load amplifier with damping-factor-control frequency compensation. IEEE J. Solid-State Circuits 35, 221–230 (2000)

R. Mita, G. Palumbo, S. Pennisi, Design guidelines for reversed nested Miller compensation in three-stage amplifiers. IEEE Trans. Circuits Syst. II 50, 227–233 (2003)

X. Peng, W. Sansen, AC boosting compensation scheme for low-power multistage amplifiers. IEEE J. Solid-State Circuits 39, 2074–2079 (2004)

X. Peng, W. Sansen, Transconductance with capacitances feedback compensation for multistage amplifiers. IEEE J. Solid-State Circuits 40, 1514–1520 (2005)

X. Peng, W. Sansen, L. Hou, J. Wang, W. Wu, Impedance adapting compensation for low-power multistage amplifiers. IEEE J. Solid-State Circuits 46, 445–451 (2011)

J. Ramos, M. Steyaert, Positive feedback frequency compensation for low-voltage low-power three-stage amplifier. IEEE Trans. Circuits Syst. I 51, 1967–1974 (2004)

Z. Yan, P.I. Mak, M.K. Law, R.P. Martins, A 0.016-mm2 144-μW three-stage amplifier capable of driving 1-to-15 nF capacitive load with 0.95 MHz GBW, in Int. Solid-State Circuits Conf, (2012), pp. 368–370

Z. Yan, P.I. Mak, M.K. Law, R.P. Martins, Ultra-area-efficient three-stage amplifier using current buffer Miller compensation and parallel compensation. IEE Electron. Lett. 48, 624–625 (2012)

F. You, S.H.K. Embabi, E. Sánchez-Sinencio, Multistage amplifier topologies with nested G m –C compensation. IEEE J. Solid-State Circuits 32, 2000–2011 (1997)

Acknowledgements

This work is supported by the National Nature Science Foundation of China (No. 61274027) and under Grant No. 51308020305.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Liao, P., Luo, P., Zhen, S. et al. Dual-Miller Parallel Compensation for Low-Power Three-Stage Amplifier with a Wide Range of Capacitive Loads. Circuits Syst Signal Process 33, 287–297 (2014). https://doi.org/10.1007/s00034-013-9626-z

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-013-9626-z