Abstract

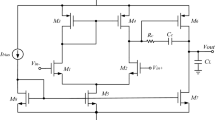

Optimizing the settling response of an operational amplifier can be a serious design issue in today’s low-power CMOS technologies. Several design challenges emerge when improving the linear and nonlinear responses of an amplifier. In this paper, we developed a settling model for use in design and optimization of two-stage Miller-compensated amplifiers. Using this model, the closed-form relations between settling time/settling error, gain-bandwidth product, noise, power and stability have been obtained. These relations are employed to form a settling-based design routine for Miller-compensated amplifiers. Simulation results in 0.18-\(\upmu \)m CMOS validate the effectiveness of the proposed routine. In a design prototype, it predicts the settling time with an error less than 3 %. In another design example, the relationship between settling time and gain-bandwidth has been evaluated with an accuracy higher than 95 %. The proposed design routine is used to implement a 40 MS/s sample-and-hold amplifier. It achieves a settling time and signal-to-noise-plus-distortion ratio equal to 12.5 ns and 82 dB, respectively.

Similar content being viewed by others

References

S. Ali, S. Tanner, P. Farine, in Design and analysis of a power-efficient cascode-compensated amplifier. IEEE Systems-on-Chip Conference, pp. 96–99 (2012).

H. Aminzadeh, MOSFET-only pipelined analogue-to-digital converters: non-linearity compensation by digital calibration. Int. J. Electron. 101, 158–173 (2014)

H. Aminzadeh, Three-stage nested-Miller-compensated operational amplifiers: analysis, design, and optimization based on settling time. Int. J. Circuit Theory Appl. 39, 573–587 (2011)

H. Aminzadeh, M. Danaie, W. Serdijn, Hybrid cascode feedforward compensation for nano-scale low-power ultra-area-efficient three-stage amplifiers. Microelectron. J. 44, 1201–1207 (2013)

H. Aminzadeh, R. Lotfi, K. Mafinezhad, in Area-efficient low-cost low-dropout regulators using MOS capacitors. IEEE Systems-on-Chip Conference, pp. 1–4 (2008).

H. Aminzadeh, R. Lotfi, K. Mafinezhad, Low-dropout voltage reference: an approach to low-temperature-sensitivity architectures with high drive capability. IET Electron. Lett. 45, 1200–1201 (2009)

F.A. Amoroso, A. Pugliese, G. Cappuccino, in Large-signal settling optimization of SC circuits using two-stage amplifiers with current-buffer Miller compensation. IEEE Conference on PhD Research in Microelectronics and Electronics, Cork, Ireland, pp. 328–331 (2009).

F.A. Amoroso, A. Pugliese, G. Cappuccino, G. Cocorullo, in Slewing investigation and improved design rules for SC circuits employing two-stage amplifiers with current-buffer Miller compensation. IEEE Conference on PhD Research in Microelectronics and Electronics, Cork, Ireland. pp. 209–212 (2008).

C. Azzolini, P. Milanesi, A. Boni, in Accurate transient response model for automatic synthesis of high-speed operational amplifiers. IEEE International Symposium on Circuits and Systems, pp. 5716–5719 (2006).

D.M. Binkley, Tradeoffs and Optimization in Analog CMOS Design (Wiley, New York, 2008)

E. Cherry, Nested differentiating feedback loops in simple audio power amplifier. J. Audio Eng. Soc. 30, 295–305 (1982)

S.S. Chong, P.K. Chan, Cross feedforward cascode compensation for low-power three-stage amplifier with large capacitive load. IEEE J. Solid-State Circuits 47, 2227–2234 (2012)

C.T. Chuang, Analysis of the settling behavior of an operational amplifier. IEEE J. Solid-State Circuits 17, 74–80 (1982)

A. Feldman, High-speed, low-power Sigma-Delta Modulators for RF base-band channel applications, Ph.D. Dissertation, University of California, Berkeley, 1997.

G. Giustolisi, in Two-stage OTA design based on settling-time constraints. IEEE International Symposium on Circuits and Systems, pp. 469–472 (2007).

R.C. Ionel, S. Ionel, A. Ignea, Calculation of the second order settling time in SISO linear systems. Circuits Syst. Signal Process. 32, 375–385 (2013)

B.Y. Kamath, R.G. Meyer, P.R. Gray, Relationship between frequency response and settling time of operational amplifier. IEEE J. Solid-State Circuits 9, 47–352 (1974)

K.N. Leung, P.K.T. Mok, Analysis of multistage amplifier frequency compensation. IEEE Trans. Circuits Syst. I 48, 1041–1056 (2001)

A. Marques, Y. Geerts, M. Steyaert, W. Sansen, in Settling time analysis of third-order systems. IEEE Intrnational Conference on Electronics, Circuits and Systems, pp. 505–508 (1998)

G. Palmisano, G. Palumbo, S. Pennisi, Design procedures for two-stage CMOS OTAs: A tutorial. Analog Integ. Circuits Signal Process. 27, 179–189 (2001)

A. Pugliese, F.A. Amoroso, G. Cappuccino, G. Cocorullo, Settling time optimization for two-stage CMOS amplifiers with current-buffer Miller compensation. IET Electron. Lett. 43, 1257–1258 (2007)

B. Razavi, Design of Analog CMOS Integrated Circuits (McGraw-Hill, New York, 2001)

J. Ruiz-Amaya, M. Delgado-Restituto, A. Rodriguez-Vazquez, Accurate settling-time modeling and design procedures for two-stage Miller-compensated amplifiers for switched-capacitor circuits. IEEE Trans. Circuits Syst. I 56, 1077–1087 (2009)

J. Ruiz-Amaya, J.F. Fernandez-Bootello, M. Delgado-Restituto, in Design procedure for optimizing the power consumption of two-stage Miller compensated amplifiers in SC circuits. European Conference on Circuit Theory and Design, pp. 452–455 (2007).

S. Seth, B. Murmann, Settling time and noise optimization of a three-stage operational transconductance amplifier. IEEE Trans. Circuits Syst. I 60, 1168–1174 (2013)

Z. Yan, P.I. Mak, M.K. Law, R.P. Martins, Ultra-area-efficient three-stage amplifier using current buffer Miller compensation and parallel compensation. IET Electron. Lett. 48, 624–626 (2012)

Z. Yan, P.I. Mak, R.P. Martins, Two-stage operational amplifiers: power-and-area-efficient frequency compensation for driving a wide range of capacitive load. IEEE Circuits Syst. Mag. 11, 26–42 (2011)

H.C. Yang, D.J. Allstot, Considerations for fast settling operational amplifiers. IEEE Trans. Circuits Syst. 37, 326–334 (1990)

Y. Yang, D.M. Binkley, C. Li, in Using moderate inversion to optimize voltage gain, thermal noise, and settling time in two-stage CMOS amplifiers. IEEE International Symposium on Circuits and Systems, pp. 432–435 (2012).

I.A. Young, in Analog mixed-signal circuits in advanced nano-scale CMOS technology for microprocessors and SoCs. European Solid-State Circuits Conference, pp. 61–70 (2010).

Acknowledgments

The authors are grateful to all contributors of this research work. This work was supported in part by National Elite Foundation, Tehran, Iran.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Aminzadeh, H., Banihashemi, M. Miller Compensation: Optimal Design for Operational Amplifiers with a Required Settling Time. Circuits Syst Signal Process 33, 2675–2694 (2014). https://doi.org/10.1007/s00034-014-9774-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-014-9774-9