Abstract

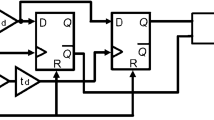

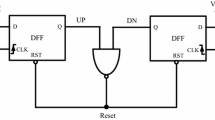

In this paper, a new design of a low-power and high-frequency phase frequency detector (PFD) is presented. Due to delay in the reset path, blind zone and dead zone, the maximum operating frequency in conventional PFDs is limited. The proposed structure uses two D flip-flops in true single-phase clock (TSPC) logic and an AND gate in gate-diffusion input (GDI) logic. Using just 16 transistors in this new structure achieves lower power consumption, and a short delay in the reset path enables the PFD to work at higher frequencies. The proposed circuit is simulated in Taiwan Semiconductor (TSMC) 0.18-µm complementary metal-oxide semiconductor (CMOS) technology. The simulated reset delay time is 150 ps in which the presented PFD operates at 3.33 GHz. The power consumption is 110 µW at a frequency of 3.33 GHz. Also, a delay locked loop (DLL) using the proposed PFD is simulated to approve the correct performance of the designed circuit at maximum frequency of 3.33 GHz. The power consumption of the presented DLL is 1.68 mW at this frequency.

Similar content being viewed by others

References

W.H. Chen, M.E. Inerowicz, B. Jung, Phase frequency detector with minimal blind zone for fast frequency acquisition. IEEE Trans. Circuits Syst. II Express Briefs 57(12), 936–940 (2010)

H. Cho, H. Lee, J. Bae, H.J. Yoo, A 5.2 mW IEEE 802.15. 6 HBC standard compatible transceiver with power efficient delay-locked-loop based BPSK demodulator. IEEE J. Solid-State Circuits 50(11), 2549–2559 (2015)

Y.S. Choi, D.H. Han, Gain-boosting charge pump for current matching in phase-locked loop. IEEE Trans. Circuits Syst. II Express Briefs 53(10), 1022–1025 (2006)

M. Gholami, Phase detector with minimal blind zone and reset time for GSamples/s DLLs. Circuits Syst. Signal Process. 36(9), 3549–3563 (2017)

M. Gholami, G. Ardeshir, Analysis of DLL jitter due to voltage-controlled delay line. Circuits Syst. Signal Process. 32(5), 2119–2135 (2013)

M. Gholami, G. Ardeshir, Jitter of delay-locked loops due to PFD. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 22(10), 2176–2180 (2014)

A. Homayoun, B. Razavi, Analysis of phase noise in phase/frequency detectors. IEEE Trans. Circuits Syst. I Regul. Pap. 60(3), 529–539 (2013)

H. Kim, Y. Kim, T. Kim, H.J. Ko, S. Cho, A 2.4-GHz 1.5-mW digital multiplying delay-locked loop using pulsewidth comparator and double injection technique. IEEE J. Solid-State Circuits 52(11), 2934–2946 (2017)

A. Koithyar, T.K. Ramesh, A faster phase frequency detector using transmission gate-based latch for the reduced response time of the PLL. Int. J. Circuit Theory Appl. 46(4), 842–854 (2018)

S.S. Kuncham, M. Gadiyar, S. Din, K.K. Lad, T. Laxminidhi, A novel zero blind zone phase frequency detector for fast acquisition in phase locked loops, in 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), 2018 Jan 6 (pp. 167–170). IEEE

W.H. Lee, J.D. Cho, S.D. Lee, A high speed and low power phase-frequency detector and charge-pump, in Innull 1999 Jan 18 (p. 269). IEEE

S. Levantino, G. Marucci, G. Marzin, A. Fenaroli, C. Samori, A.L. Lacaita, A 1.7 GHz fractional-N frequency synthesizer based on a multiplying delay-locked loop. IEEE J. Solid-State Circuits 50(11), 2678–2691 (2015)

B. Razavi, TSPC logic [a circuit for all seasons]. IEEE Solid-State Circuits Mag. 8(4), 10–13 (2016)

A. Rezaeian, G. Ardeshir, M. Gholami, Low-power and wide-band delay-locked loop with switching delay line. Int. J. Circuit Theory Appl. 46(12), 2189–2201 (2018)

K. Ryu, D.H. Jung, S.O. Jung, Process-variation-calibrated multiphase delay locked loop with a loop-embedded duty cycle corrector. IEEE Trans. Circuits Syst. II Express Briefs 61(1), 1–5 (2014)

K. Ryu, D.H. Jung, S.O. Jung, A DLL with dual edge triggered phase detector for fast lock and low jitter clock generator. IEEE Trans Circuits Syst. Regul. Pap. 59(9), 1860–1870 (2012)

G.Y. Tak, S.B. Hyun, T.Y. Kang, B.G. Choi, S.S. Park, A 6.3-9-GHz cmos fast settling PLL for MB-OFDM UWB applications. IEEE J. Solid-State Circuits 40(8), 1671–1679 (2005)

Y. Wang, Y. Liu, S. Jia, X. Zhang, Delay-locked loop based clock and data recovery with wide operating range and low jitter in a 65-nm CMOS process. Int. J. Circuit Theory Appl. 45(6), 851–858 (2017)

Y. Zhao, Z.Z. Chen, Y. Du, Y. Li, R. Al Hadi, G. Virbila, Y. Xu, Y. Kim, A. Tang, T.J. Reck, M.C. Chang, A 0.56 THz phase-locked frequency synthesizer in 65 nm CMOS technology. IEEE J. Solid-State Circuits 51(12), 3005–3019 (2016)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rezaeian, A., Ardeshir, G. & Gholami, M. A Low-Power and High-Frequency Phase Frequency Detector for a 3.33-GHz Delay Locked Loop. Circuits Syst Signal Process 39, 1735–1750 (2020). https://doi.org/10.1007/s00034-019-01232-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-019-01232-9